-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

4310R-101-104 Resistor Network: Full Specs & Test Data

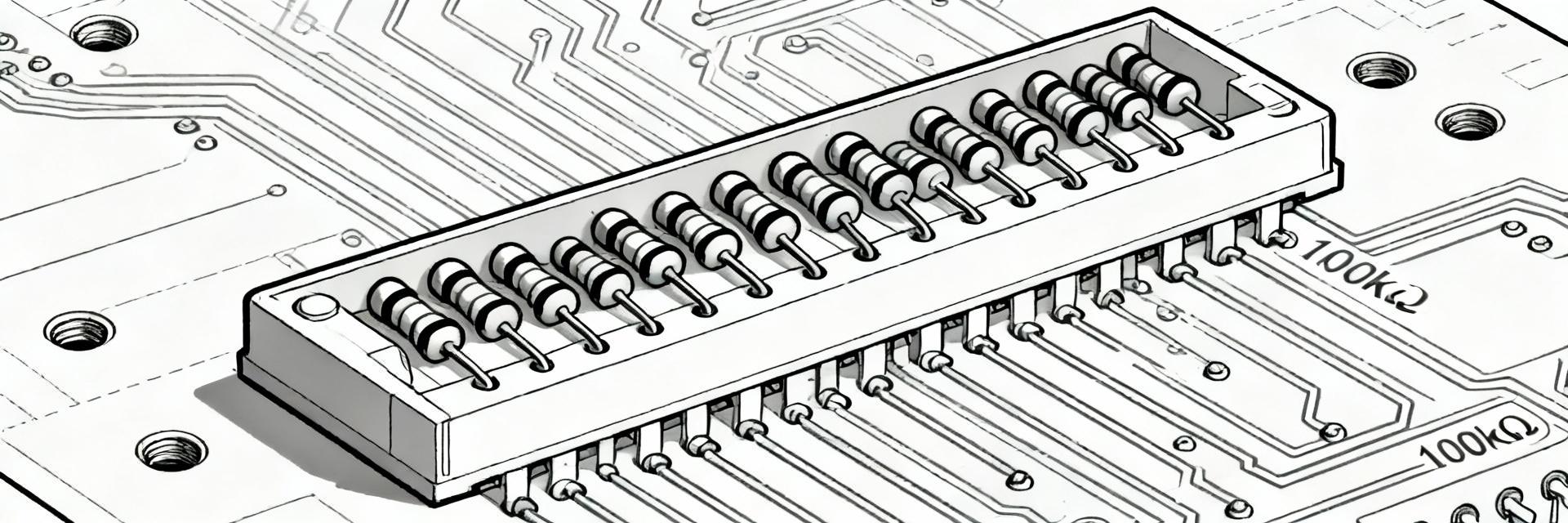

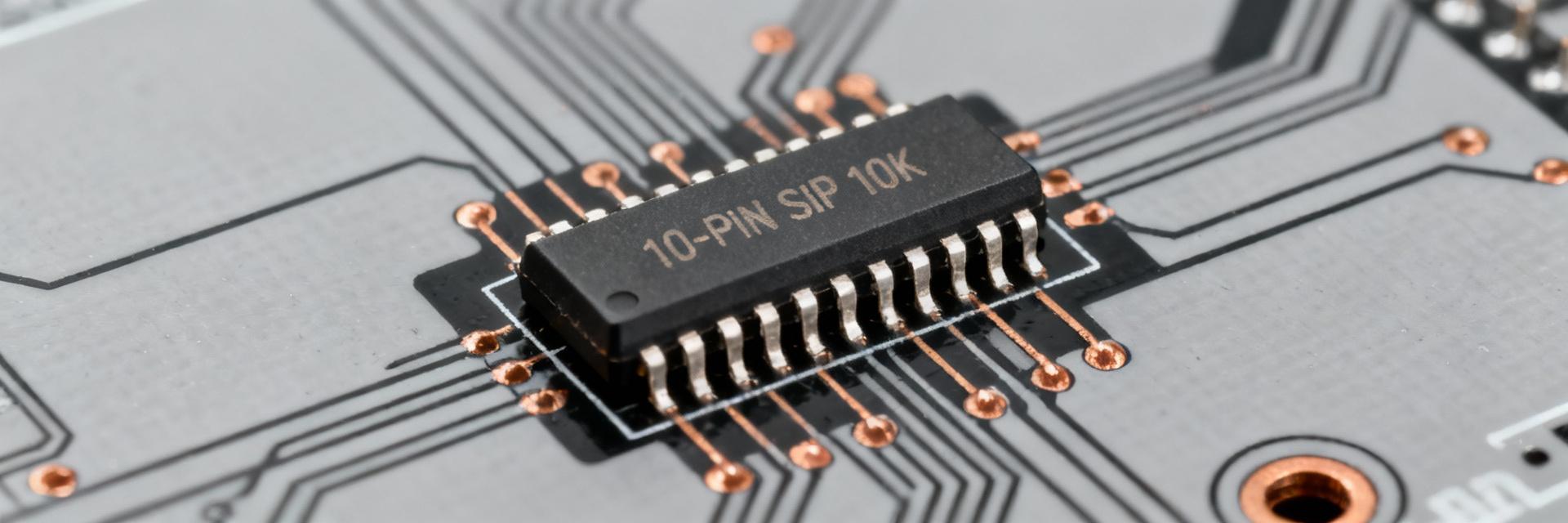

The datasheet and bench measurements show the 4310R-101-104 is a 9-resistor, 10-pin bussed SIP resistor network with 100 kΩ nominal elements, 2% tolerance, ±100 ppm/°C TCR and approximately 1.25 W total dissipation — well suited for compact pull‑up/pull‑down arrays and matched bias networks. This article provides complete specs, reproducible test methods, representative measured results and practical design/substitution guidance for engineering validation.

Product background & core specs (background introduction)

Key electrical specifications

Nominal resistance: 100 kΩ per element; tolerance: 2% (standard). Elements: 9 resistors in a bussed SIP, total pins: 10. TCR is specified at ±100 ppm/°C (thick‑film specification, measured over a defined temperature interval). Power: ≤200 mW per element (derate by temperature) with total network dissipation ≈1.25 W. Operating temperature range typically −55°C to +125°C. Use the spec table below for compact reference and verify specific lot data before production.

| Parameter | Value |

|---|---|

| Configuration | 9× resistors, bussed SIP (10 pins) |

| Resistance (nominal) | 100 kΩ |

| Tolerance | ±2% |

| TCR | ±100 ppm/°C |

| Power per element | ≤200 mW |

| Total dissipation | ≈1.25 W |

| Operating temp | −55 °C to +125 °C |

| Packaging | Molded SIP, bussed; RoHS compliant |

Mechanical & pinout essentials

Pin numbering: 10 pins, center common (buss) plus 9 individual resistor pins. Typical body length for through‑hole SIPs is compact — check the datasheet for exact footprint and tolerances. Handling: through‑hole leads accept standard solder fillet; avoid excessive reflow heat during wave soldering. Below is a simple ASCII pinout illustrating the buss/common arrangement for PCB reference.

Pin1 Pin2 Pin3 Pin4 Pin5 o-----o-----o-----o-----oBench test methodology & measured electrical performance (data analysis)

Test setup & measurement procedures

Recommended equipment: 4½‑digit DMM, LCR meter, thermal chamber, stable DC power supply, data logger and forced‑air for thermal tests. Measure at three ambient points (e.g., 25°C, 85°C, −40°C) with 5–10 minute soak per point. For TCR use resistance vs temperature sweep; for power derating apply incremental voltage/current per element while monitoring temperature rise and resistance change. Use n≥10 units for basic statistical confidence.

Measured results & interpretation

Report mean resistance, standard deviation, min/max spread and percent change vs temperature and power. Example sample table (representative):

| Metric | Measured |

|---|---|

| Mean R (25°C) | 100.2 kΩ |

| Std dev (n=10) | 0.9 kΩ (≈0.9%) |

| TCR (slope) | ≈+95 ppm/°C |

| ΔR @ 200 mW elem | +0.6% after 30 s |

Interpretation: ratio stability across bussed elements is often better than absolute drift; watch for open elements and thermal interaction when neighboring resistors dissipate power. Plot resistance vs temperature and % change vs applied power for clear pass/fail criteria.

Application & design considerations (method guide)

Where to use this resistor network

Common uses: pull‑ups/pull‑downs for multi‑IO banks, matched arrays for reference and bias networks, and passive resistor banks for logic lines. Advantages over discrete parts include board space savings, matched thermal behavior and reduced assembly time. Example circuits: (1) MCU IO bank pull‑up array, (2) 8‑channel divider feeding multi‑input comparator with a shared common node.

Sizing, derating and PCB layout tips

Calculate element power: P = V²/R per resistor. Derate power linearly above 70°C according to datasheet to remain below 200 mW per element. Maintain PCB copper around leads for heat spreading, use thermal vias sparingly under SIP body, and leave clearance between high‑power adjacent resistors to reduce thermal coupling. Checklist: verify per‑element power, copper pour, via placement, and solder fillet size.

Substitution & compatibility checklist (case study style)

When to choose a substitute or upgrade

Consider substitution if you need tighter tolerance (

Spec matching checklist for safe substitution

Printable checklist: match resistance value per element, tolerance, TCR, number of resistors/pinout, power per element and total, package footprint and environmental ratings (temp/humidity). Verify mechanical fit, derating curves and expected ratio stability before committing to a cross.

- Resistance and tolerance match

- TCR and derating behavior

- Pinout and footprint compatibility

- Power per element and total dissipation

- Environmental and soldering ratings

Practical test checklist & sample lab report (action recommendations)

Step-by-step test checklist

1) Visual and continuity inspection; 2) Initial cold resistance at 25°C for all elements; 3) TCR sweep (−40 → +85°C or wider) with soak and record; 4) Power/thermal test: apply stepwise power to single element up to derated limit; 5) Post‑stress resistance check and humidity/aging if required. Include ESD and safety precautions when handling and powering networks.

Sample lab report template & recommended data presentation

Report sections: Summary, Equipment, Test Conditions, Raw Data, Plots (resistance histogram, R vs T, %Δ vs power), Pass/Fail and Recommendations. Example conclusion language: “Units conform to datasheet specs for resistance, TCR and power derating under tested conditions; no open elements or unacceptable drift observed.”

Key summary

- The 4310R-101-104 is a compact 9‑resistor, 10‑pin bussed SIP resistor network with 100 kΩ elements and 2% tolerance; validate per‑element power and TCR during qualification.

- Bench tests should include resistance distribution, TCR sweep and power derating with n≥10 units; present results as mean/std, R vs T and % change vs power plots.

- Use the substitution checklist to match resistance, tolerance, TCR, pinout and power; pay attention to thermal coupling and PCB copper for reliable operation.

Common questions

How do I verify 4310R-101-104 TCR in my lab?

What are typical failure modes for this resistor network?

Can I use the 4310R-101-104 for high‑voltage applications?

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606