-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

RSL10X331G SIP-10 Resistor Network: Complete Datasheet Guide

The RSL10X331G SIP-10 resistor network is a compact, nine-element array in a single 10‑pin package used for pull‑ups, matched networks, and terminations in space‑ and cost‑sensitive embedded designs. Engineers habitually verify datasheet entries—resistance, tolerance, TCR, power per element, and pinout—when selecting a part. This guide provides a practical, line‑by‑line walkthrough of the datasheet to speed evaluation and implementation.

This article focuses on actionable extraction of critical numbers from the datasheet, mechanical confirmations for PCB layout, and example calculations for TCR and power derating. Key terms used throughout include SIP-10 resistor network and datasheet; the short part name appears to identify the subject quickly for procurement and verification.

1 — Background: What the RSL10X331G Is and Why It Matters

What "SIP-10 resistor network" means

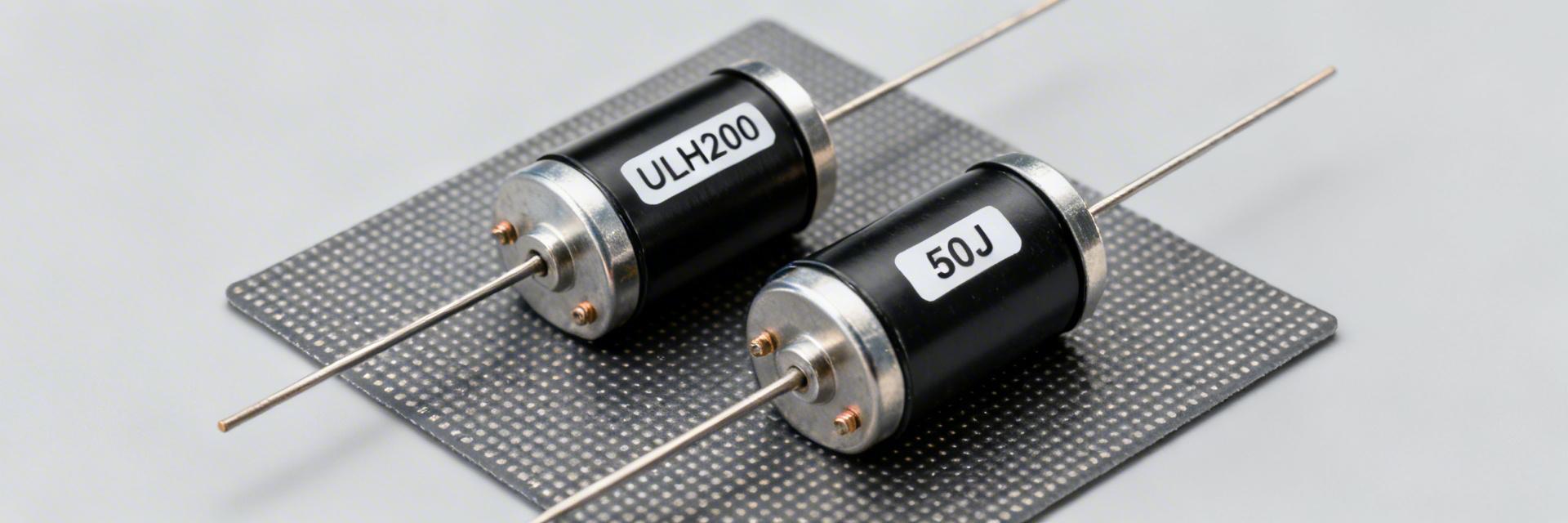

A SIP-10 resistor network is a single in‑line package with ten pins that typically houses nine discrete resistor elements. Common topologies are bussed (one common pin plus multiple resistors) and isolated (each element independent). Compared to nine discrete resistors, a SIP-10 saves PCB area and simplifies BOM and placement, reducing assembly time and mismatch risk.

Typical use cases in modern US embedded designs

Designers use SIP-10 networks for microcontroller GPIO pull‑ups/pull‑downs, matched resistor pairs for differential sensor inputs, and line terminations. Benefits include consistent matching between elements, lower parasitics than discrete chains, simplified routing, and fewer placement errors—advantages that translate into smaller PCBs and lower unit costs in high‑volume assemblies.

2 — Quick Datasheet Snapshot: Essential Specs & Pinout (data-analysis)

Electrical spec checklist to extract immediately

From the datasheet extract: nominal resistance value, tolerance, TCR (ppm/°C), max working voltage, element power rating (W), and resistance stability/aging. Confirm units and test conditions (25°C reference, ± tolerance). These numbers determine drift, noise contribution, voltage stress limits, and whether the network suits low‑drift or high‑speed applications.

Mechanical & pinout data to confirm before layout

Verify package dimensions, pin pitch, seated height, recommended PCB footprint, and encapsulation material on the datasheet. Confirm pin mapping for bussed vs. isolated topologies—misreading the pinout can convert a bussed array into an unintended short across signals and cause functional failures on board.

| Quick Specs | Typical Value / Notes |

|---|---|

| Resistance | 330 Ω nominal (example family) |

| Tolerance | ±1% / ±2% / ±5% options |

| TCR | ±200 ppm/°C (typical variants) |

| Power per element | 0.125 W typical (check derating) |

| Package | SIP-10 molded; 2.54 mm pitch |

| Pin | Function (example bussed) |

|---|---|

| 1 | Resistor 1 |

| 2 | Resistor 2 |

| 10 | Common bus |

3 — Electrical Characteristics & Performance Interpretation (data-analysis)

How to read and interpret resistance, tolerance, and TCR tables

Nominal resistance is specified at 25°C; tolerance is the allowable deviation (e.g., ±1%). TCR (ppm/°C) predicts change with temperature: a 200 ppm/°C TCR yields ΔR/R = 200×10⁻⁶ × ΔT. Across −40°C to +85°C (ΔT = 125°C) a 200 ppm/°C device shifts ≈0.025 or 2.5% of nominal resistance, important for precision sensor fronts ends.

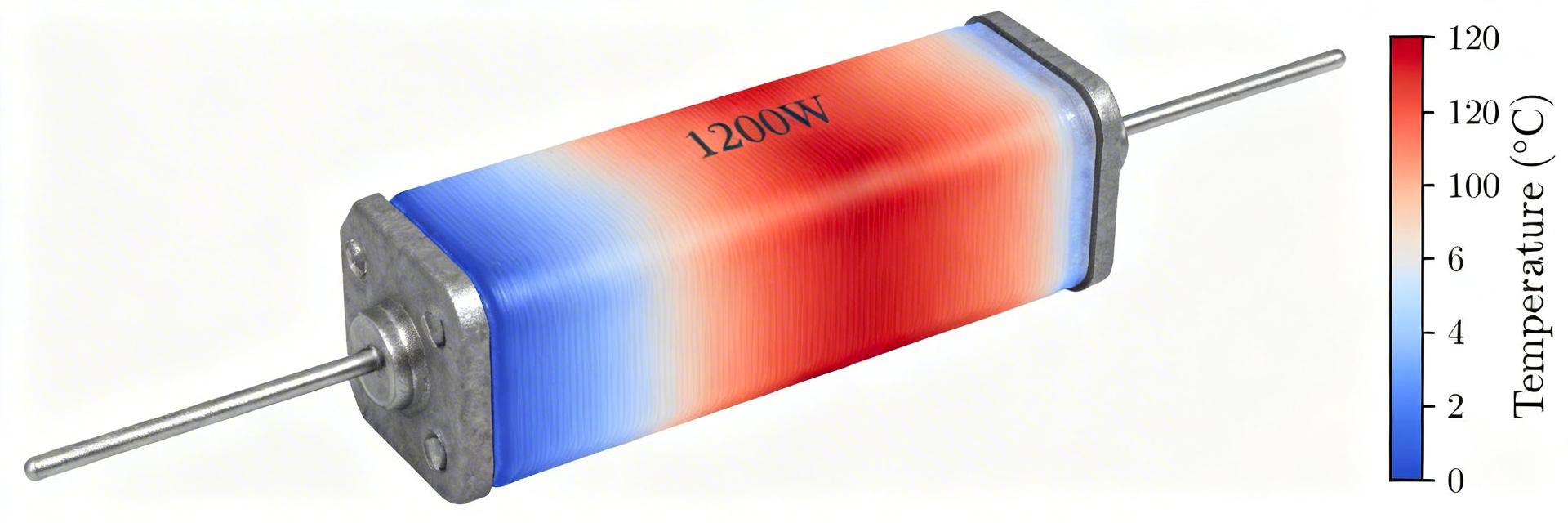

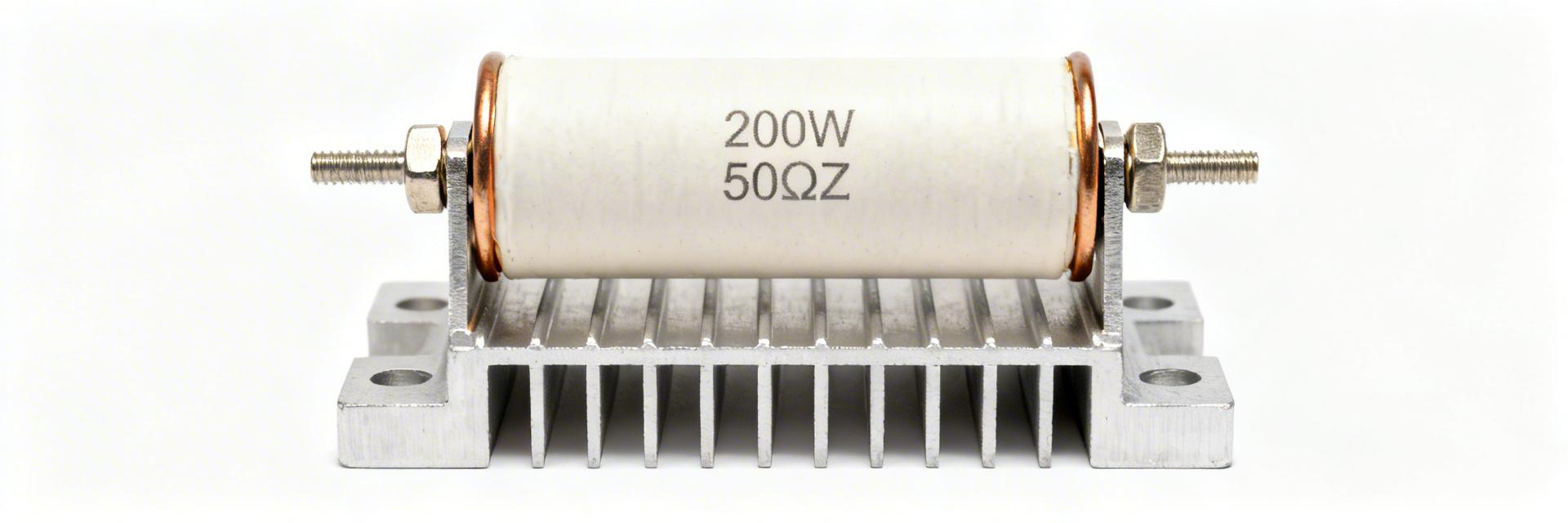

Power handling, derating, and reliability factors

Per‑element power ratings are given at specified ambient and PCB conditions (e.g., 0.125 W at 70°C). Use the datasheet derating curve: P_allowed = P_rated × derate_factor(ambient). Account for thermal coupling: adjacent elements heat each other, reducing continuous power capability. For safe continuous operation, apply a conservative derate and validate with board thermal measurements.

4 — Design & PCB Integration Guide (method-guide)

Footprint, soldering and thermal considerations

Follow recommended pad geometry and solder‑mask expansion from the datasheet to avoid tombstoning and poor fillets. Adhere to the supplier's reflow profile and avoid excessive mechanical stress during assembly. For through‑hole or wave solder processes, confirm lead finish and post‑solder mechanical integrity in pre‑production samples.

Layout patterns for signal integrity and matching

Place the SIP-10 close to the device pins it serves to minimize trace length and parasitic inductance. For matched networks, route symmetric traces and keep pair lengths equal. For pull‑ups, use a short, direct route to the MCU pin and a single bypass or decoupling strategy for nearby pins to reduce common‑mode noise coupling.

5 — Typical Circuits & Application Examples (case-study)

Pull-up/pull-down network examples for microcontroller GPIOs

Common pull‑up values range from 4.7 kΩ to 47 kΩ; lower values reduce susceptibility to noise and speed up edges but increase power when asserted. A bussed SIP-10 simplifies applying uniform pull‑ups to multiple GPIOs while keeping trace routing tidy; include ESD protection components as required by the IO specification.

Matched-array examples: sensor bridges and termination

Use isolated elements when individual matching or trimming is needed; use bussed topologies for common reference pull‑ups. For differential inputs, matched pairs from the same SIP-10 improve thermal tracking and reduce drift versus discrete resistors mounted apart.

Bussed pull-ups (schematic): MCU_PIN1 ---/\/\/\--- Pin1 (330Ω) MCU_PIN2 ---/\/\/\--- Pin2 (330Ω) Common Vcc ----- Pin10

Matched bridge (concept):

Sensor+ --/\/\/\--+--/\/\/\-- Sensor-

| |

Ref node Ref node

6 — Procurement, Part Numbering & Pre‑Production Checklist (action-guide)

Decoding the part number and selecting variants

Confirm nominal resistance, tolerance, packaging (tube/reel), lead finish, temperature grade, and ordering code in the datasheet and distributor tables. If a suffix meaning is ambiguous, consult the datasheet ordering table. Maintain a cross‑reference checklist to prevent ordering the wrong topology or tolerance at scale.

Qualification & testing checklist before production

Recommended pre‑production tests: sample electrical verification at temperature extremes, solderability tests, mechanical inspection, and thermal cycling for reliability. Define pass/fail criteria (e.g., resistance within specified tolerance after 100 cycles). Document lot acceptance criteria and traceability for each component reel or tube.

Summary

- Confirm key datasheet entries: nominal resistance, tolerance, TCR, max working voltage, and per‑element power—these determine electrical suitability and long‑term stability for the RSL10X331G.

- Validate mechanical fit: pin pitch, seated height, and recommended footprint to avoid layout errors and assembly issues; double‑check pinout for bussed vs. isolated variants.

- Apply conservative thermal derating, consider thermal coupling between elements, and run pre‑production electrical and solderability tests to ensure production readiness.

Frequently Asked Questions

How do I verify resistance stability from the datasheet?

Check resistance tolerance, TCR, and stability/aging specifications listed under electrical characteristics. Use the TCR to estimate drift over your operating range and include expected aging or stability figures. Validate with sample parts at temperature extremes and after thermal cycling to confirm real‑world behavior.

What footprint and pad guidelines should I follow for SIP-10 packages?

Use the recommended footprint from the datasheet: 2.54 mm pin pitch, correct pad length and solder‑mask expansion, and the manufacturer’s recommended land pattern. Follow reflow profile guidance to avoid tombstoning and ensure reliable solder joints.

When should I choose isolated elements over a bussed SIP-10 network?

Choose isolated elements when individual matching, trimming, or separate reference connections are required. Use bussed networks for uniform pull‑ups or where sharing a common node reduces BOM and layout complexity; always verify the pinout to ensure the intended topology.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606