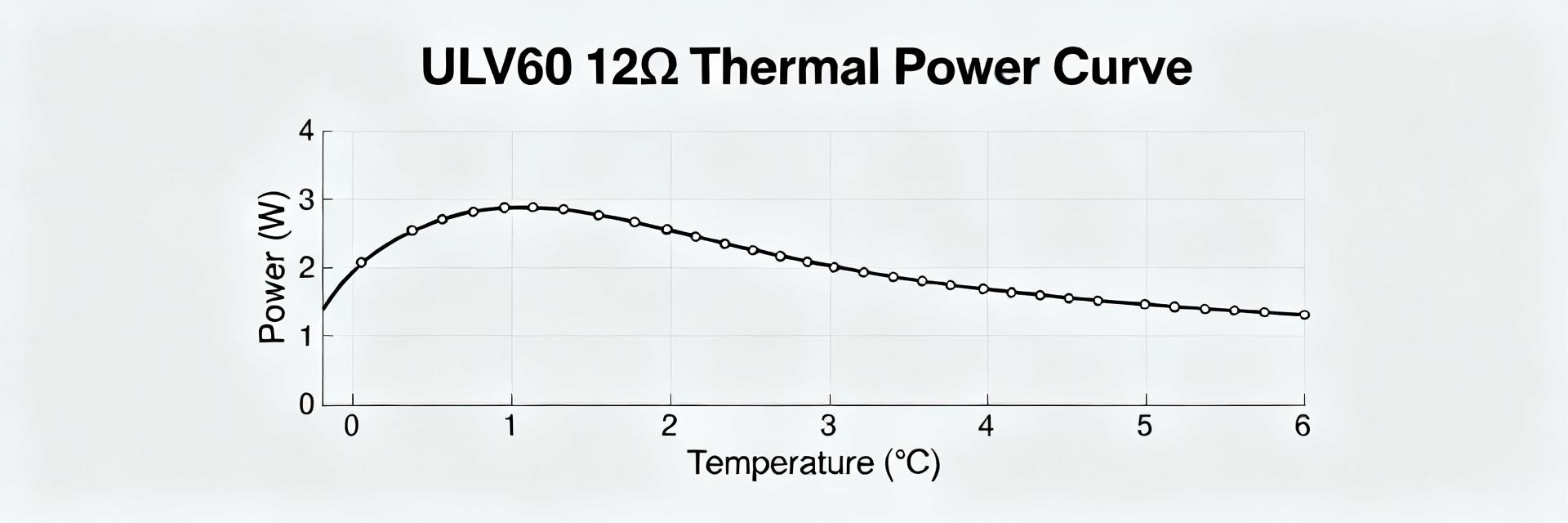

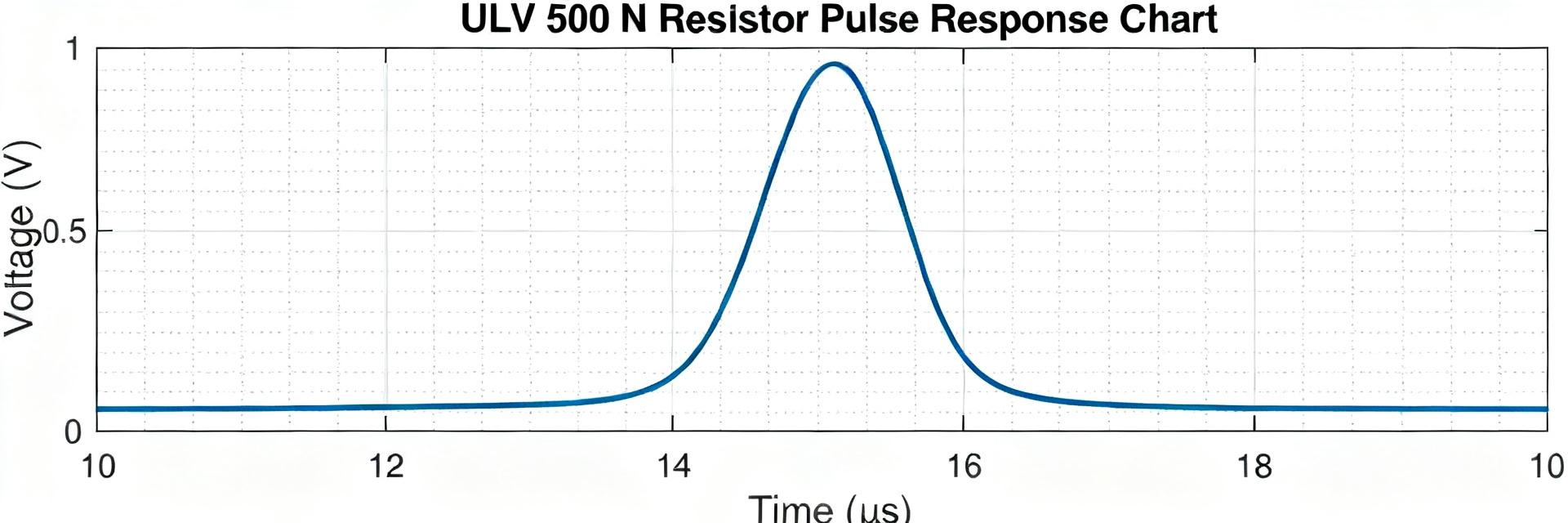

Reading the ULV 500 N 0.4 J datasheet accurately is a practical necessity for reliable systems: a mistaken continuous power assumption or a misread pulse‑energy limit can turn a high‑duty resistor into a rapid failure point. Typical design numbers to watch are continuous dissipation in the single to low hundreds of watts, and pulse energies in the sub‑joule to multi‑joule range — both affect cooling and duty cycles. This article decodes the ULV 500 N datasheet so engineers can interpret electrical specs, thermal limits, and selection constraints with confidence. It emphasizes the datasheet sections to prioritize, worked formulas for voltage/current/power, pulse handling examples, and a compact verification checklist engineers can use in the lab. 1 Product overview & datasheet layout (Background) Figure 1: ULV 500 N Resistor Series Technical Layout 1.1 — What the ULV 500 N is (quick functional summary) The ULV 500 N is a high‑energy, power‑dissipation resistor family intended for dynamic braking, snubbing, or short‑duration load absorption in power electronics. Functionally it is a resistive element optimized for absorbing pulse energy and steady dissipation in confined form factors. On the datasheet, flag electrical specs, pulse‑energy charts, thermal‑derating graphs and mechanical dimensions as the critical sections to locate. 1.2 — How to read this datasheet: sections that matter most Rated resistance & tolerance table — use for nominal current/voltage calculations and tolerance stacking. Continuous power rating and power vs. ambient derating curve — gives safe steady‑state dissipation. Pulse energy (J) charts and pulse duration limits — essential for transient handling. Thermal resistance, time constants and thermal mass notes — for transient heating checks. Mechanical and mounting data — screw torque, clearance, and recommended airflow. Common misreads: confusing peak pulse power with continuous rating; ignoring repetition rate for pulses. 2 Electrical specifications decoded (Data analysis) 2.1 — Resistance, tolerance, and temperature coefficient: what they mean in application Nominal resistance and tolerance set the expected V/I range: V = I·R and P = V·I = I²·R. Tolerance (e.g., ±5%) changes worst‑case current at a given voltage; account for tolerance when sizing fuses and drivers. Temperature coefficient (ppm/°C) shifts resistance with temperature; for example, a +200 ppm/°C rise over 50°C increases R by ~1.0%, altering dissipation and balance in series/parallel networks. Use the datasheet specs to recompute operating points at elevated temperatures. 2.2 — Rated continuous power vs. pulse ratings: practical interpretation Continuous power rating is the steady dissipation the part can handle at a specified ambient and mounting condition. Pulse (Joule) ratings indicate the energy the resistor can absorb in one transient without exceeding thermal limits. Example: for a 0.4 J allowed single pulse, a pulse delivering Ppulse for t seconds must satisfy E = Ppulse·t ≤ 0.4 J. For repetitive pulses, account for recovery time; if duty cycle prevents full thermal recovery, derate pulse energy by a safety margin (typical margin 20–50%). 3 Thermal behavior & limits (Data analysis) 3.1 — Thermal resistance, ambient conditions, and derating curves Datasheet thermal resistance (°C/W) links power to temperature rise: ΔT = Pdiss·θ. Read the power vs. ambient curve to find allowed Pdiss at your ambient. Step: pick ambient Tamb, look up allowed P on the derating plot, or compute Tmax = Tamb + Pdiss·θ and ensure Tmax stays below material limits. When ambient rises, allowable continuous power falls roughly linearly on many curves — apply the curve rather than linear guesses. 3.2 — Transient heating: energy absorption, time constants, and safe pulse handling Pulse handling relies on thermal time constant τ and pulse duration tp. If tp ≪ τ, the resistor behaves as a thermal mass and tolerates higher instantaneous energy; use the J rating or pulse‑duration chart instead of steady‑state rating. Example: a 10 ms pulse with I²R giving 0.3 J is acceptable if the J curve shows ≥0.3 J at 10 ms. For repetitive pulses, ensure average power (E·repetition_rate) plus steady load stays under continuous capability with margin (20–30%). 4 Mechanical, mounting & environmental constraints 4.1 — Mounting, airflow, and clearance requirements Mounting orientation and airflow materially change cooling. Use datasheet mounting notes (screw torque, pad isolation, clearance) and place resistors to maximize convective flow. ✔ DO Follow recommended torque Provide 10–20 mm clearance Ensure convective flow ✘ DON'T Enclose without forced cooling Rely on chassis alone Ignore vibration ratings 4.2 — Vibration, ingress protection, and ambient limits Verify operating temperature range and listed vibration/IP ratings against your environment. If datasheet lists, for example, −40 to +125°C and vibration N standard, confirm your shock/vibration spectrum matches. For harsh environments, require parts with sealed encapsulation or higher IP and add conformal coating or potting only after confirming it won’t trap heat and invalidate thermal limits. 5 Measurement, verification, and selection checklist 5.1 — Lab test protocol to validate datasheet claims Test plan: steady‑state test at planned ambient with calibrated load and thermocouples on resistor body, measure surface temperature vs. time until steady. Pulse test: apply single pulse of known energy, capture peak temperature with thermal camera, then apply repetitive pulses at intended duty cycle and log temperature rise. Safety: start at 50% of rated energy, use remote switching and current limiting, and record failure modes for root‑cause analysis. 5.2 — Component selection flow: matching ULV 500 N specs to system requirements Compute continuous Pdiss and required pulse energy. Add 20–50% safety margin for pulses. Add 20–30% for continuous derating at high ambient. Verify mechanical fit and mounting torque. Check tolerance and TC for circuit tolerance budget. 6 Common failure modes & troubleshooting 6.1 — Typical field failures linked to misinterpreted specs Common root causes: underrating continuous power (overheating), ignoring pulse repetition rate (thermal accumulation), inadequate airflow or improper mounting (elevated temps), and tolerance/TC mismatch (unexpected currents). Signs include discoloration, intermittent resistance drift, open‑circuit failures shortly after high‑energy events, and hotspots on thermal scans. 6.2 — Quick remediation steps and design changes Immediate fixes: reduce applied energy, increase cooling or airflow, add thermal gap pads or heatsinking, derate voltage/current. Long‑term: choose a higher J‑rated variant, increase safety margins, redesign snubber networks to reduce pulse energy, or distribute dissipation across multiple parts to lower per‑part stress. Summary Decoding the ULV 500 N 0.4 J datasheet is about matching continuous and transient specs to real‑world duty, reading thermal curves correctly, and validating with measurement. Focus on resistance/tolerance/TC, continuous power derating, and pulse J ratings; verify mounting and environmental constraints; and use lab tests to confirm safe operation before deployment. Key Takeaways Check resistance, tolerance and TC to set correct V/I and power margins; recalculated values must feed design protection and balancing. Use power vs. ambient derating curves to size continuous dissipation and apply a 20–30% safety derate in marginal environments. Interpret pulse J charts with pulse duration and repetition rate; for repetitive pulses derate pulse energy by 20–50% and validate with thermal imaging tests. FAQ What is the safe pulse energy for ULV 500 N 0.4 J per the datasheet? Datasheet pulse limits depend on pulse duration; a stated 0.4 J single‑pulse rating means a pulse delivering E = P·t ≤ 0.4 J at the referenced duration is acceptable. Always confirm the pulse‑duration curve and apply a conservative margin (20–50%) for repeated pulses or uncertain cooling conditions. How should I derate continuous specs for ULV 500 N 0.4 J in higher ambient? Use the power vs. ambient derating graph: find your ambient, read allowed Pdiss, and then apply an additional 20–30% margin for unexpected thermal coupling or reduced airflow. If no curve exists for your mounting, perform a steady‑state test to determine real thermal performance. What lab tests validate ULV 500 N 0.4 J datasheet claims? Validate with steady‑state power soak tests and controlled single/repetitive pulse tests. Instrument with calibrated current/voltage probes, surface thermocouples, and a thermal camera. Start at reduced energy (≈50% rated), ramp to intended levels, log temperatures, and compare to datasheet curves; stop if surface temperatures approach material limits.