-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

Complete L101S471LF Datasheet: Full Specs & Pinout

The L101S471LF datasheet consolidates the essential parameters designers need when choosing a 10‑pin resistor network: nine 470 Ω resistors, ±2% tolerance, ~100 ppm/°C temperature coefficient, bussed configuration, and ~0.125 W power per resistor. These numbers directly affect noise, bias currents, thermal derating and placement decisions on compact PCBs, so a single-reference datasheet speeds accurate design and review.

This article covers electrical specs, mechanical dimensions, a clear pinout, example wiring patterns, PCB/layout and test tips aimed at hardware engineers and PCB designers. It presents quick calculations and checklist items so readers can convert the L101S471LF data into safe operating margins and practical layouts within a concise technical summary.

1 — What the L101S471LF Is (Background)

Key specs at a glance

- Resistor value: 470 Ω nominal (each of nine resistors)

- Tolerance: ±2% (specification block in datasheet electrical table)

- Configuration: 10‑pin SIP, bussed common pin, nine resistors

- Power per resistor: ~0.125 W typical (lookup in power rating section)

- Temperature coefficient: 100 ppm/°C (listed in environmental/temperature table)

These entries typically appear in the datasheet overview, electrical characteristics table and mechanical drawing; confirming each location avoids selection errors during BOM review.

Typical applications

The L101S471LF is commonly used for grouped pull‑ups or pull‑downs on MCU port banks, simple signal termination, and sensor interface bias networks. Long‑tail search targets include phrases like “resistor network for MCU pull‑ups” and “resistor array 10‑pin SIP for I/O bias,” reflecting its typical role in embedded systems and compact analog grouping.

2 — Complete Electrical Specifications (Data & How to Use Them)

Resistance, tolerance and temperature coefficient

Nominal resistance is 470 Ω; ±2% tolerance means actual value = 470 Ω ±9.4 Ω. With 100 ppm/°C, the drift from −40 to +85 °C (a 125 °C span) is 470 Ω × 100×10⁻⁶ ×125 ≈ 5.9 Ω, so worst‑case over temperature adds roughly 1.25% to the base tolerance. Use this to size precision circuits and set comparator thresholds.

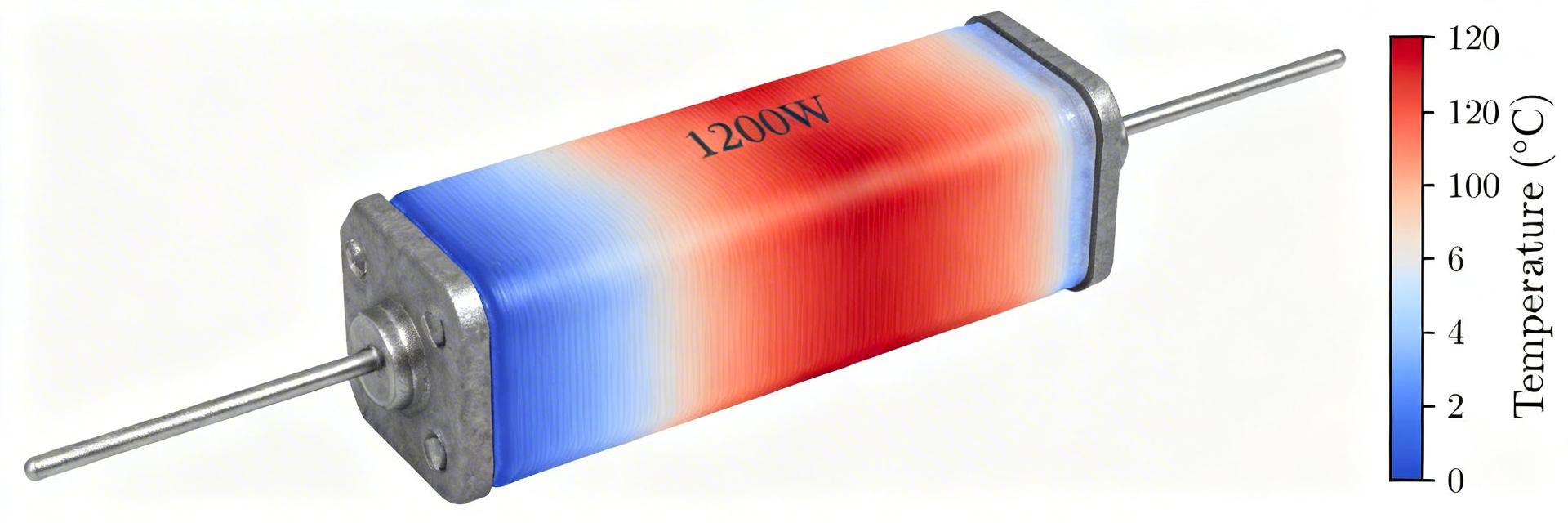

Power rating and derating guidance

Each resistor is rated at ~0.125 W. For a single resistor, allowable continuous current I = sqrt(P/R) = sqrt(0.125/470) ≈ 0.0163 A (16.3 mA). On a populated PCB, derate for elevated ambient and reduced airflow—apply linear derating from rated temp to maximum operating temp per datasheet derating curve and avoid running resistors near their max power in parallel configurations unless thermal modelling confirms safe junction rise.

3 — Mechanical, Pinout & Thermal Details (Package & Pinout)

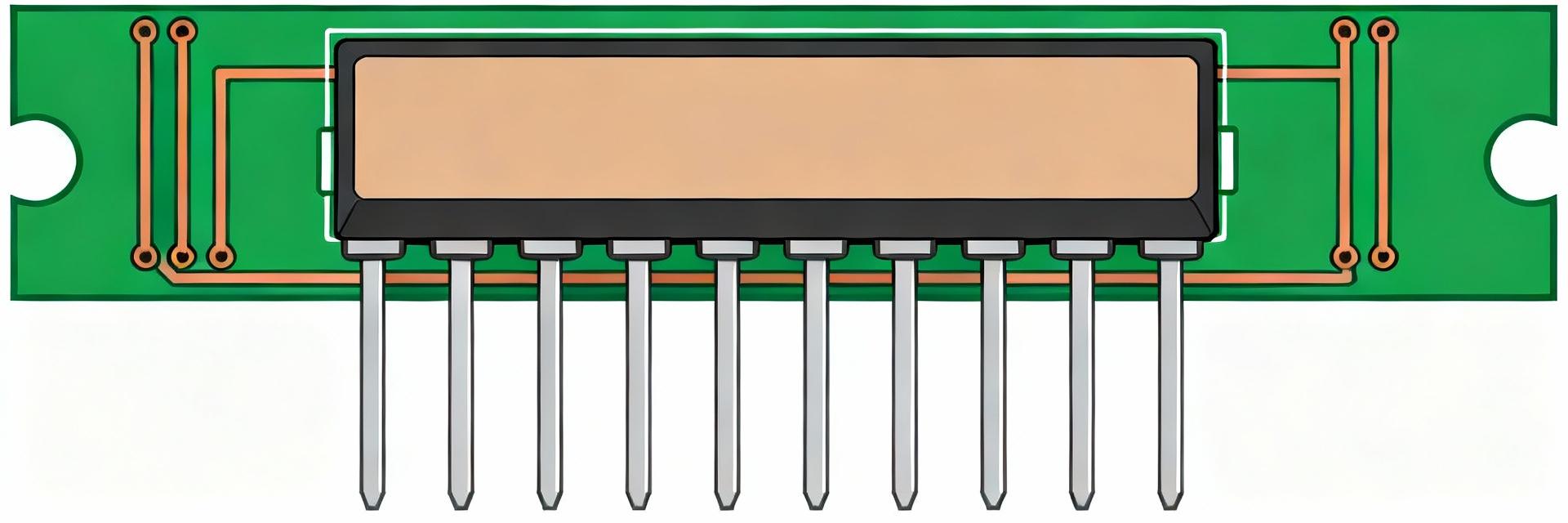

Package dimensions and footprint guidance

Key mechanical parameters to note: 10‑pin SIP body length, pin pitch (typically 2.54 mm), body height and lead length. Recommended PCB footprint items include 2.54 mm pitch holes, 0.8–1.0 mm plated through‑hole drill, and annular rings sized per board house rules. Check the datasheet drawing for exact tolerances before final artwork.

Pinout diagram and pin functions

Pin mapping: a 10‑pin SIP with one common (bussed) pin and nine individual resistor end pins. Textual mapping example: Pin 1 = resistor1 end A, Pins 2–10 = resistor ends B and the common (depending on manufacturer orientation). Use the label “common” for the bus pin and verify orientation notch when converting to a silk‑screened diagram.

4 — How to Read the L101S471LF Datasheet (Practical Guide)

Interpreting electrical tables and tolerances

Datasheet tables show typical vs maximum columns—typical values are representative, maximum are guaranteed limits. Confirm test conditions (ambient temperature, measurement circuit) printed in the table footnotes. Treat limits as the guaranteed safe spec; use typicals only for approximate modelling and margining.

Finding substitution/variant info and ordering tips

Variants differ by resistance value, tolerance code, or temperature coefficient suffixes. When seeking drop‑in substitutes, match package, pinout polarity (bussed vs isolated), R value, tolerance and power rating. Always confirm revision level and ordering code suffixes in the official datasheet before placing an order.

5 — Example Circuits & Wiring Patterns (Case Studies)

Bussed vs. isolated resistor configurations

For bussed pull‑ups tie the common pin to VCC and each resistor end to individual I/O lines; this creates uniform pull‑up resistance across lines. For isolated networks, each resistor is independent—useful for voltage dividers or matched termination. Text schematic: COMMON → VCC; R1 ←→ IO1, R2 ←→ IO2, etc.

Typical use-cases: pull-ups, voltage dividers, and termination

Pull‑up example: with 470 Ω to VCC (3.3 V), steady current per line = 3.3/470 ≈ 7.0 mA; ensure total bus current and power stay below derated limits. For a divider, pair 470 Ω with another resistor; check loading effects on signal integrity and place the array close to the MCU pins for best performance.

6 — Design & Test Checklist (Actionable next steps)

PCB layout, thermal and Soldering best practices

Checklist: verify footprint and drill sizes, include thermal relief for through‑holes, allow spacing for heat dissipation, orient part number/marking toward test probes, and use standard lead‑free solder profiles. Consider conformal coating only after thermal verification; coatings can trap heat and affect dissipation.

Measurement and troubleshooting tips

Testing steps: measure each resistor in‑circuit with power removed; look for expected resistance ±2% and common continuity on bus pin. Under power, verify voltages and use thermal imaging or touch testing for hot spots. Common failures include solder cracks, incorrect pin wiring and localized overheating from excessive bus current.

Summary

Key takeaways: the L101S471LF datasheet defines nine 470 Ω resistors in a 10‑pin SIP bussed package with ±2% tolerance, 100 ppm/°C tempco and ~0.125 W per resistor—data critical for biasing and termination. Consult the full L101S471LF datasheet for exact mechanical drawings and absolute maximum ratings before layout and procurement.

- Electrical fundamentals: 470 Ω, ±2% tolerance and 100 ppm/°C—use these to set precision and drift margins in circuits.

- Mechanical and pinout: 10‑pin SIP, 2.54 mm pitch; verify footprint drill and orientation before PCB release.

- Thermal & power: 0.125 W per resistor; calculate I = sqrt(P/R) and derate for board temperature and crowded layouts.

7 — FAQ

What is the L101S471LF datasheet key resistance and tolerance?

The L101S471LF lists nine 470 Ω resistors with a ±2% tolerance. Designers should calculate absolute tolerance: 470 Ω ±9.4 Ω, and include temperature drift from the 100 ppm/°C spec when budgeting precision across expected operating temperatures.

How is the pinout arranged for the L101S471LF pinout?

The 10‑pin SIP has a single common (bussed) pin and nine individual resistor ends. Orientation markers on the package define Pin 1; map Pin 1 through Pin 10 according to the datasheet drawing to place the common on the correct net when converting text mapping to a PCB silk diagram.

What test steps confirm a good installation of L101S471LF?

With power off, measure each resistor to confirm value within ±2% and check common continuity on the bus pin. Power the board and measure voltages under load, inspect for hot resistors, and reflow suspect joints. Thermal imaging helps identify overloaded elements or poor solder joints quickly.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606