New Product Launch

More +

Hot Selling Parts

Blog

ULH 60 4 J Datasheet: Technical Specs Snapshot Quick Guide

A professional engineering reference for rapid decision-making and design integration.

When engineers need a go/no‑go decision fast, a one‑page technical snapshot cuts review time by orders of magnitude. This guide delivers a scannable summary of the ULH 60 4 J datasheet and shows how to apply the key sections in design, test, and procurement. It focuses on the critical entries engineers check first — rated values and test conditions, derating guidance, mechanical callouts, thermal limits, and the verification steps that prevent costly field failures.

The intent is practical: extract the most actionable items from the datasheet so teams can evaluate fit, performance, and compliance in minutes. Readers will find a concise electrical/mechanical snapshot, a data‑driven approach to derating and thermal planning, and a short procurement checklist to speed qualification and ordering.

(1) Quick snapshot: ULH 60 4 J at a glance (background introduction)

Key identifiers & part naming conventions (1)

Point: Confirm the exact part code and variant suffixes before design acceptance.

Evidence: datasheet part‑number table and revision notes typically list the complete format and any tolerated suffixes.

Explanation: Look for the base code plus any letter suffix that denotes tolerance, packing, or terminal style; verify the revision code and date code on the label to ensure the print matches the datasheet variant you evaluated.

One-line electrical & mechanical summary (1)

Point: Capture top‑line technical specs in one glance so downstream teams can triage suitability.

Evidence: the datasheet header and 'ratings' table contain the authoritative numbers.

Explanation: Create a one‑line spec bullet list — rated voltage/current/power; package and mounting; operating temperature range — so purchasers and designers can immediately filter parts.

Parameter

Snapshot

Rated voltage / current

See datasheet 'continuous rating' entry (use that value for system fit)

Power / dissipation

Datasheet power rating at reference ambient (note test conditions)

Package & mounting

Enclosure type, terminals, recommended PCB footprint

Operating range

Ambient and storage temperature limits, humidity guidance

(2) Electrical performance: detailed specs and limits (data analysis)

Rated values & test conditions (1)

Point: Rely on the datasheet's rated‑value table and the specified test conditions.

Evidence: most datasheets show continuous ratings and short‑term/peak ratings with explicit conditions such as temperature, measurement method, and frequency.

Explanation: Use continuous ratings for normal operation and peak values only for defined transient events; verify the reference ambient (commonly 25°C) and any required mounting or airflow condition attached to the rating.

Derating, tolerances & environmental limits (1)

Point: Interpret derating curves and tolerance notes to establish safe operating envelopes.

Evidence: the datasheet typically includes a derating graph and a tolerances table with temperature coefficients.

Explanation: Read the derating curve to adjust allowable power or current versus ambient. Apply tolerance and temperature coefficient (ppm/°C or %/°C) to calculate worst‑case performance; factor humidity and altitude limits into reliability margins for deployed systems.

(3) Mechanical, thermal & mounting details (method/guideline)

Package dimensions & mounting instructions (1)

Point: Mechanical callouts in the datasheet prevent assembly issues and mechanical failures. Evidence: dimensional drawings, hole‑pattern tables, and torque specifications are authoritative. Explanation: Transfer critical dimensions to the PCB footprint (hole spacing, pad size) and follow recommended torque for fasteners. Add fillets or reliefs where the datasheet warns of stress concentration and follow recommended connector stacking to avoid mechanical strain.

Thermal performance & cooling recommendations (1)

Point: Turn thermal metrics into concrete cooling steps for the system. Evidence: datasheet Rth (junction‑to‑ambient or case), thermal resistance graphs, and recommended heatsinking examples. Explanation: Calculate expected temperature rise at rated load using Rth and ambient assumptions; if junction temps exceed safe limits, specify heat‑sinking area or forced airflow (CFM) required to meet derating curves and maintain reliability.

(4) How to read the ULH 60 4 J datasheet: practical checklist (method/guideline)

Verification checklist before design approval (1)

Point: Use a short checklist to avoid missed requirements during design sign‑off. Evidence: cross‑check against datasheet tables and footnotes for exceptions and special test conditions. Explanation: Verify continuous and peak ratings, measurement temperature, thermal interfaces, mounting notes, tolerance and temperature coefficient, safety markings, and revision code. Require supplier confirmation for any ambiguous entry before approval.

Test & validation notes for lab and field (1)

Point: Define bench and in‑system tests to confirm datasheet claims under application conditions. Evidence: datasheet test procedures and suggested qualification flows inform lab validation. Explanation: Recommended tests include functional burn‑in at elevated ambient, thermal imaging under rated load, and voltage/current ramp tests for transient response. Establish pass/fail criteria tied to maximum permitted deviations in the datasheet tables.

(5) Typical applications and compatibility considerations (case study style)

Common use-cases & suitability (1)

Point: Match the part’s rated envelope to target applications and note borderline scenarios. Evidence: rated power and thermal limits determine suitability for continuous vs. intermittent duty. Explanation: Use the part in systems where continuous dissipation stays within derated limits; avoid in tightly enclosed or high‑ambient installations unless additional cooling is provided. For borderline current or power, plan revalidation and monitor thermal performance in situ.

Interfacing & substitution rules (1)

Point: Follow a conservative substitution policy that preserves margin. Evidence: datasheet tolerance and derating criteria inform allowable substitution windows. Explanation: When replacing, match or exceed power and voltage ratings, maintain equal or better thermal resistance and identical mechanical fit where possible, and revalidate system‑level tests after substitution to confirm no hidden regressions.

(6) Compliance, procurement & quick action checklist (action recommendation)

Compliance flags & labeling to confirm (1)

Point: Request documentation that proves the part meets required safety and performance marks. Evidence: the datasheet and supplier declarations typically list applicable listings and test reports. Explanation: Ask suppliers for safety certificates, test reports referenced in the datasheet, and evidence of the lot traceability; treat missing or vague documentation as a procurement red flag requiring clarification before purchase.

Purchase & inventory tips (1)

Point: Practical procurement steps reduce lead‑time and quality risk. Evidence: shelf‑life and storage notes in the datasheet or packaging spec guide handling. Explanation: Order samples for qualification, specify acceptable manufacturing dates, confirm minimum order quantity and packaging, and run a quick incoming inspection and functional spot test to catch damaged parts before board assembly.

Summary

Top‑line electrical and mechanical callouts: use the datasheet's continuous ratings and package drawing for quick go/no‑go decisions and transfer those values into schematic and PCB checks.

Derating and thermal essentials: read the derating curve and Rth values to calculate junction temperature under application load and specify cooling measures if required for safe margin.

Verification checklist: confirm ratings, test conditions, mounting requirements, and request compliance documentation before approving a part for production.

(FAQ) Common questions about extracting specs

How should engineers use the datasheet to size cooling for a part?

Use the datasheet Rth and power dissipation to compute temperature rise (DeltaT = P × Rth) relative to ambient; compare the resulting junction or case temperature to the maximum allowed. If the result exceeds limits, add heatsinking or forced airflow and re‑calculate using the datasheet's derating curve.

What immediate red flags in a datasheet mean further vendor discussion is required?

Ambiguous test conditions (missing reference ambient), absent derating curves, unclear tolerance or temperature coefficient data, and missing compliance certificates are red flags. Require the supplier to confirm or provide the missing test reports before qualification.

End of Technical Snapshot: ULH 60 4 J Reference Document

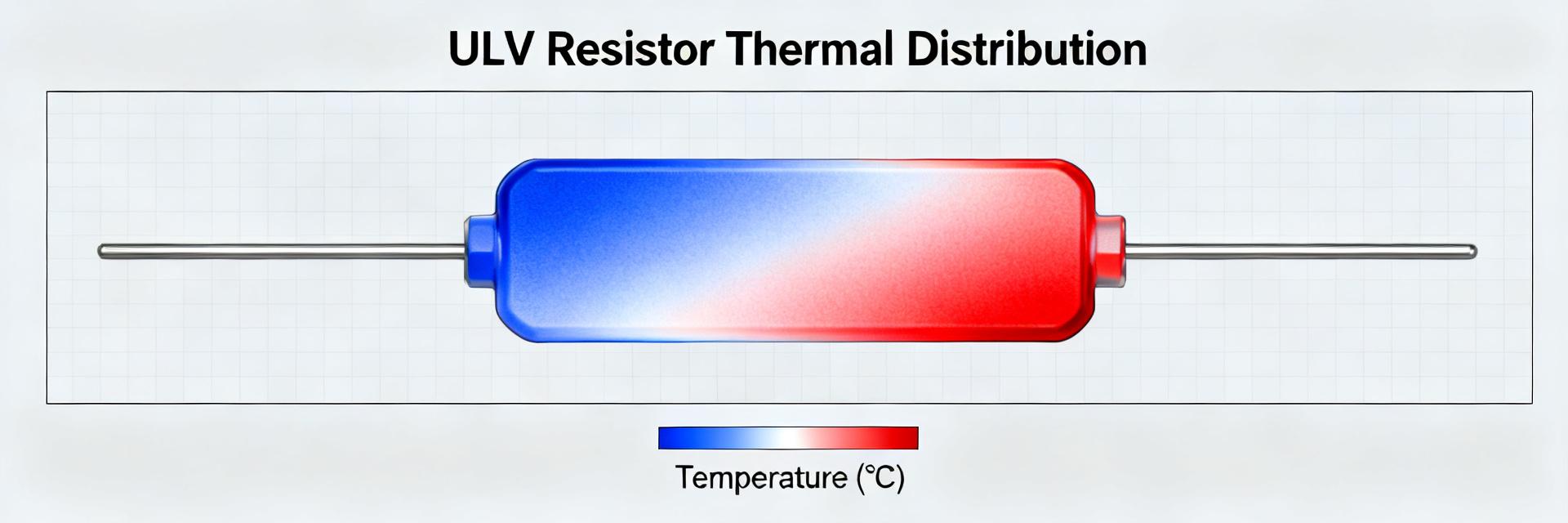

ULV Resistor Thermal Report: Datasheet Deep Dive Quick Guide

Point: Recent product surveys show a clear migration toward higher power density and compact packages in braking and load-bank designs, increasing thermal risk for compact components.

Evidence: Industry sampling indicates a double-digit rise in designs using compact ULV form-factors.

Explanation: This guide helps engineers read a ULV resistor datasheet, extract critical thermal specs, and convert those values into reliable design decisions.

Scope: Practical interpretation of datasheet entries, defining repeatable test protocols for prototype sign-off.

ULV Resistor at a Glance: Design, Use Cases, and Why Thermal Matters

What makes ULV resistors distinct

Point: ULV resistors combine compact envelopes with relatively high dissipation per unit volume.

Evidence: Typical construction uses a metal-clad housing and chassis-mount flange establishing the primary heat path.

Explanation: Chassis conduction is the dominant cooling route; designers must prioritize mounting behavior.

Key thermal failure modes

Point: Several measurable failure modes recur in field returns.

Evidence: Hotspots, exceeded insulation class, and terminal derating are common root causes.

Explanation: Exceeding 120–150°C case limits or solder ratings shortens life and raises safety risk.

How Thermal Specs Appear on a ULV Resistor Datasheet

Typical thermal spec items and what they mean

Point: Datasheets list rated power (on-chassis vs free air), thermal resistance (°C/W), and pulse energy specs.

Evidence: Each entry carries reference conditions—mounting area or air movement.

Explanation: Confirm units; listed thermal resistance usually maps case-to-ambient or case-to-chassis.

Red flags and ambiguous entries

Point: Ambiguity undermines safe design.

Evidence: Vague “operating temperature range” without test conditions is a red flag.

Explanation: Always ask: was power measured on a defined heat-sink? If airspeed is missing, lab characterization is mandatory.

Repeatable Thermal Test Methods

Test Type

Protocol Highlights

Steady-State

Mount on intended chassis, stabilize ambient ±1°C, use K-type thermocouples. Wait for equilibrium (

Pulsed & Transient

Define pulse shape (J) and duty cycle. Use high-speed data loggers to derive thermal time constant τ.

Interpreting Steady-State vs Pulsed Charts

Worked Example: Power vs. Temperature Rise

Example: 140 W On-Chassis (Rth 0.5°C/W) vs 100 W Free-Air (Rth 0.9°C/W).

On-Chassis: 70°C Rise

Free-Air: 90°C Rise

Explanation: At 40°C ambient, On-Chassis case ≈ 110°C; Free-Air case ≈ 130°C. This helps check insulation class limits.

Pulse Energy (E = C·ΔT): Short pulses (t

Practical Examples & Common Pitfalls

Example A: Continuous Braking

120 W with 0.6°C/W = 72°C rise. At 35°C ambient, case ≈107°C. Acceptable if insulation class ≥130°C.

Common Pitfall

Designers often use free-air ratings for chassis-mounted parts or confuse pulse vs steady ratings. Validate with lab tests.

Engineer’s Quick Selection & Verification Checklist

Pre-selection Checklist

✅ Confirm rated power (Chassis vs Free Air)

✅ Check Thermal Resistance (°C/W)

✅ Max Case/Terminal temperatures

✅ Verify Pulse Specs vs Energy (J)

Field Verification Plan

📋 Instrumentation: K-type TCs & Calibrated IR

📋 Pass/Fail: Case temp

📋 Archive TC locations and timestamps

Summary

Point: Align datasheet thermal specs to real mounting and duty conditions.

Evidence: Matching °C/W, derating curves, and time-constant behavior prevents surprises.

Call to Action: Use the checklist and test plan to reduce thermal risk before prototype sign-off; validate ambiguous entries experimentally.

Extract and confirm thermal specs—rated power reference and thermal resistance.

Use steady-state and pulse test protocols with calibrated TCs.

Compute pulse allowance from time-constant or E = C·ΔT formula.

Frequently Asked Questions

How should an engineer interpret ULV resistor pulse ratings?

Answer: Convert pulse specs to a common energy metric (Joules). If durations or voltage/current are specified, perform a fixed-energy pulse test to confirm temperature rise if conditions differ from the datasheet.

What is the best way to convert thermal resistance into case temperature?

Answer: Use ΔT = P × Rth. Multiply power by thermal resistance to get the temperature rise, then add your ambient temperature to find the final case temperature.

When is laboratory verification mandatory?

Answer: Mandatory whenever datasheet conditions (mounting area, airspeed) differ from your real profile. Run tests replicating real use to establish pass/fail criteria before production sign-off.

ULV Resistor Thermal Report - Technical Engineering Guide

ULV1000 resistor: Latest Thermal Data & Derating Guide

2026-05-13 10:24:19

ULV 150 Resistor Deep Report: Thermal Specs & Tests

2026-05-12 10:16:20

ULV60 12Ω Datasheet: Power Specs & Thermal Curve Guide

2026-05-10 10:15:19

ULV 500 N Datasheet Analysis: Key Specs & Limits Explained

2026-05-07 10:26:17

ULV80 Resistor Data Report: Specs, Thermal & Size Guide

2026-05-06 10:17:15

Read more