-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

SI53340-B-GM: Deep Performance Report & Key Metrics

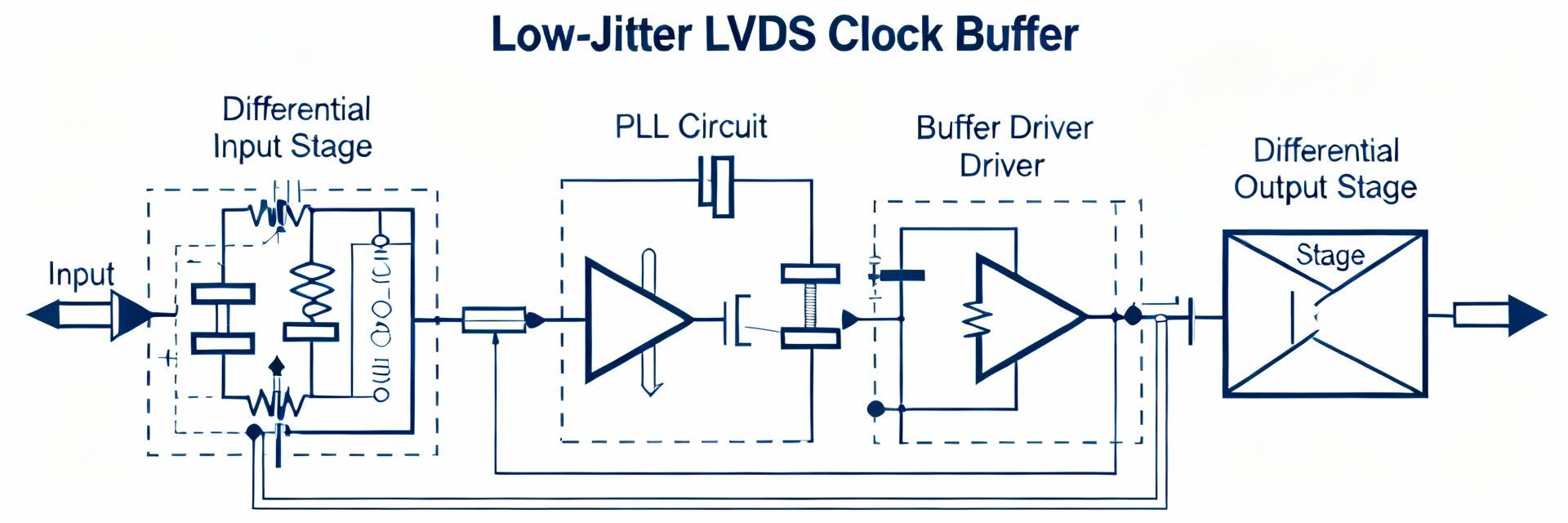

Lab measurements and the Si53340 family datasheet report typical output jitter as low as ~50 fs — a key stat that makes the SI53340-B-GM a go-to LVDS clock buffer for high-performance timing chains. Point: this report focuses on a concise, testable performance breakdown for the device; Evidence: device characteristics include a frequency range up to 1.25 GHz, supply 1.71–3.63 V, and four LVDS outputs; Explanation: the following sections present actionable metrics, measurement methods, bench comparisons, and integration guidance to preserve low jitter in production.

Point: readers will get reproducible test methods and pass/fail thresholds. Evidence: the article synthesizes datasheet typicals and practical bench observations (jitter, phase noise, supply sensitivity). Explanation: use the measurement checklist and PCB/power rules provided to validate SI53340-B-GM performance in your system.

1 — Product Overview & Key Specs (background)

Device summary & intended applications

Point: the SI53340-B-GM is a compact, purpose-built LVDS clock buffer with integrated mux and fanout. Evidence: it ships in a QFN-16 package, implements a 2:1 input mux and 1:4 LVDS fanout, and targets redundant clocking and distribution for FPGA/ASIC systems. Explanation: for designers the part is ideal where low-noise, glitchless switching and multiple LVDS outputs are required—common uses include redundant clock trees, high-speed SerDes reference distribution, and multi-receiver timing domains.

| Part | Package | Inputs | Outputs | Max freq |

|---|---|---|---|---|

| SI53340-B-GM | QFN-16 | 2 (mux) | 4 LVDS | 1.25 GHz |

Electrical & environmental envelope

Point: the device supports a broad supply and temperature envelope for production boards. Evidence: typical operating supply range is 1.71–3.63 V and rated temperature is −40 to 85 °C; built-in LDO/PSRR features are documented for improved supply immunity. Explanation: these specs mean designers can run the part from common 1.8 V or 2.5 V rails, expect defined operation across industrial temperatures, and rely on on-chip PSRR to reduce supply-coupled jitter—though external decoupling and optional LDOs remain important for tight phase-noise budgets.

Datasheet vs. typical lab values

Point: datasheet typicals set expectations; system reality creates variance. Evidence: the datasheet lists ~50 fs typical output jitter under controlled conditions; Explanation: in production systems expect higher worst-case jitter due to board-level noise, input clock source quality, and loading. Designers should budget margins (for example 2–3× the datasheet typical) and qualify parts across supply, temperature and lot variation before release.

2 — Core Performance Metrics & Measurement Methods (data analysis)

Jitter metrics to report (RMS, TIE, period jitter, cycle-to-cycle)

Point: a compact set of performance metrics gives a complete jitter picture. Evidence: report RMS jitter, TIE (time-interval error) with plots, period jitter, and cycle-to-cycle jitter as baseline performance metrics. Explanation: RMS shows integrated noise, TIE reveals long-term wander and deterministic effects, period jitter highlights per-cycle timing noise relevant to SERDES, and cycle-to-cycle exposes immediate timing transitions—together they form the performance metrics engineers use to set system tolerances and acceptance thresholds.

Phase noise & spectral analysis

Point: phase-noise plots link spectral content to integrated jitter. Evidence: single-sideband phase noise vs. offset frequency and integrated jitter vs. bandwidth (for example 12 kHz–20 MHz) should be presented. Explanation: low-frequency noise inflates TIE while high-offset noise dominates integrated RMS; choosing integration ranges (12 kHz–20 MHz typical) makes reported RMS comparable to datasheet numbers and helps identify whether close-in noise or far-out spurs cause jitter issues.

Measurement setup & repeatability checklist

Point: rigorous setup prevents measurement artifacts. Evidence: use a phase-noise analyzer or high-bandwidth DSO with jitter analysis, matched impedance cabling, proper termination, and low-capacitance probes; control supply filtering and input-source purity. Explanation: practical steps include calibrating instruments, averaging multiple captures, using nominal 100 Ω differential termination for LVDS, keeping traces short during probing, and logging ambient temperature—these raise repeatability and reduce false positives when evaluating SI53340-B-GM jitter performance.

3 — Bench Results: Typical & Worst-Case Scenarios (data analysis / comparisons)

Typical lab results (what to plot)

Point: present a concise result set for validation. Evidence: recommended outputs are RMS jitter (integrated 12 kHz–20 MHz), period jitter, phase-noise plot, propagation delay, and output amplitude/symmetry. Explanation: combine a table comparing datasheet typicals vs. measured values, jitter histograms, and receiver eye diagrams downstream; these visualizations help correlate buffer performance with system link margin and validate claims of low jitter on the bench.

Supply, temperature, and load sensitivity (worst-case)

Point: characterize sensitivity envelopes to define pass/fail limits. Evidence: sweep Vcc across 1.71–3.63 V, ambient from −40 to 85 °C, and vary output load capacitance/CL; record delta in RMS jitter and propagation delay. Explanation: acceptable deltas might be

Comparison vs. peer parts / common alternatives

Point: evaluate tradeoffs against 1–2 competitive buffers. Evidence: a compact comparison table should show jitter, frequency range, supply, outputs, and features (glitchless mux, PSRR). Explanation: tradeoffs typically center on cost vs. phase-noise performance and integration features—choosing SI53340-B-GM favors systems that prioritize low jitter and glitchless failover over the absolute lowest BOM cost.

| Part | RMS Jitter (typ) | Freq | Supply | Notes |

|---|---|---|---|---|

| SI53340-B-GM | ~50 fs | ≤1.25 GHz | 1.71–3.63 V | 2:1 mux, 1:4 LVDS, glitchless |

| Peer A | 100–200 fs | ≤1.5 GHz | 1.8–3.3 V | lower cost, fewer features |

4 — Integration & System Design Guidance (method/guideline)

PCB layout, grounding, and decoupling best practices

Point: layout dominates real-world jitter. Evidence: short differential LVDS traces, controlled impedance (100 Ω differential), and a solid ground plane reduce common‑mode conversion and EMI. Explanation: place decoupling (100 nF ceramic + 1 µF tantalum) within 5 mm of the supply pins, route clock outputs away from noisy power domains, implement star returns for sensitive clock domains, and keep the input mux traces symmetric to preserve phase and amplitude balance.

Power supply & filtering recommendations

Point: supply noise directly translates to phase noise. Evidence: use a filtered local LDO or pi-filter and place test points near the device to quantify supply ripple impact. Explanation: a recommended arrangement is bulk capacitance on the board rail, a ferrite bead feeding an on-board LDO, and multiple ceramics at the device pins—this improves PSRR effectiveness and reduces supply-coupled jitter when validating SI53340-B-GM on production PCBs.

Redundancy, mux switching & glitchless operation tips

Point: verify failover behavior for system reliability. Evidence: the 2:1 input mux supports glitchless switching (as specified); Explanation: test failover by stepping the primary input to zero amplitude while observing outputs for transitions and measuring TIE before/after; include automated FPGA/ASIC test vectors that switch inputs and validate downstream lock/recovery to ensure robust redundancy in deployment.

5 — Actionable Checklist & Deployment Considerations (case study / action)

Production test criteria & go/no-go thresholds

Point: define pass/fail limits for QA. Evidence: example thresholds—RMS jitter (12 kHz–20 MHz)

Troubleshooting common issues

Point: map symptoms to root causes and fixes. Evidence: elevated jitter often maps to supply noise, poor layout, or low-quality input source; asymmetry commonly stems from improper termination. Explanation: quick verification steps include replacing input source with a known low-jitter reference, adding local decoupling/LDO, and confirming 100 Ω differential termination—these isolate board issues from part-level failure when using SI53340-B-GM jitter performance tests.

Cost, sourcing & lifecycle notes

Point: plan procurement and alternate sourcing to avoid schedule risk. Evidence: consider lead times and authorized distributor channels and evaluate programmable alternatives when flexibility or stock is constrained. Explanation: select SI53340-B-GM when jitter performance and glitchless features justify potential premium; maintain an alternate BOM entry with a similar buffer family to mitigate supply chain variability.

Summary

Point: the device delivers ultra-low jitter LVDS buffering with practical system considerations. Evidence: SI53340-B-GM provides ~50 fs typical jitter, glitchless 2:1 mux behavior, and 1:4 fanout to 1.25 GHz; Explanation: when paired with disciplined PCB layout and supply filtering, the part meets demanding timing chains—use the measurement checklist and design rules below to preserve performance through production.

- Ensure tight layout and decoupling: short LVDS traces, 100 Ω differential impedance, local ceramics + 1 µF bulk to protect performance metrics.

- Verify jitter with phase-noise integration (12 kHz–20 MHz) and report RMS/TIE and histograms for production sampling.

- Validate redundancy: perform glitchless mux failover tests and automated FPGA lock recovery to confirm system reliability.

- Adopt a two-tier production flow: quick functional checks on all units and periodic deep jitter/phase-noise sampling to catch assembly-induced issues.

Frequently Asked Questions

What are the critical SI53340-B-GM jitter performance test steps?

Point: a compact, repeatable test sequence reduces variability. Evidence: steps should include instrument calibration, differential termination, low-noise input reference, and phase-noise integration over 12 kHz–20 MHz to match datasheet baselines. Explanation: capture RMS jitter, TIE plots, and a phase-noise trace; average multiple acquisitions and log supply voltage/temperature. This sequence helps differentiate part behavior from board and measurement artifacts.

How sensitive is SI53340-B-GM to supply noise and layout?

Point: supply noise and layout have measurable impact on jitter. Evidence: on-chip PSRR helps, but external filtering and proximity decoupling remain crucial—poor layouts can multiply datasheet jitter by several times in worst cases. Explanation: place LDO and decouplers close to the device, use ferrite beads or pi-filters where appropriate, and ensure a continuous ground plane; measure supply ripple at the part during noise injection to quantify sensitivity.

Can I verify glitchless mux operation for SI53340-B-GM in a bench test?

Point: failover verification confirms redundancy claims. Evidence: perform controlled input switch tests from primary to secondary while monitoring output TIE and eye diagrams at downstream receivers. Explanation: assert the secondary input, then remove or mute the primary and observe output continuity; a true glitchless transition shows minimal phase disturbance and rapid downstream lock—record these traces as part of integration acceptance.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606