-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

F3L600R10N3S7FBPSA1 Datasheet: Full Specs & Ratings

The F3L600R10N3S7FBPSA1 delivers top-tier power density for three‑level inverter designs — rated for high blocking voltage and hundreds of amperes of continuous current — making it suitable for traction, industrial drives and renewable inverters. This data‑first guide breaks the datasheet into actionable sections: family background, decoded part string, a compact specs table, how to read and verify datasheet numbers, an example 3‑level power stage design, and a bench validation checklist.

Background & what the part number means

Module family and intended use

Point: This module belongs to the high‑power IGBT module class designed for three‑level topologies. Evidence: modules in this class are optimized around series/parallel cell arrangements and integrated half‑bridge layouts. Explanation: three‑level topologies reduce dv/dt and switching stress, yielding lower switching losses and higher efficiency at medium voltage ranges, which benefits traction inverters, large motor drives and PV/energy storage inverters.

Decoding the part number and versions

Point: The part string encodes voltage class, current capability and package variant; suffixes denote mechanical or sensor options. Evidence: typical decoding maps a leading family code to IGBT generation, numeric groups to voltage/current class, and trailing letters to packaging or added features. Explanation: always check suffixes for thermistor presence, mounting style and busbar options; confirm exact mechanical drawing and ordering code before layout and procurement.

F3L600R10N3S7FBPSA1 — Key electrical, thermal & mechanical specs (data analysis / full specs)

Electrical ratings & switching specs (spec tables)

Point: Key electrical specs determine suitability for system voltage, continuous current and switching performance. Evidence: representative datasheet values (verify against the manufacturer's datasheet for final design):

| Parameter | Typical / Rated Value | Test conditions |

|---|---|---|

| Vces / VCEO | 1200 V (blocking) | − |

| IC (continuous) | 335 A (per module, Tc = 100°C) | case temperature specified |

| IC (peak, pulsed) | ~1200 A (short pulse) | tp, duty per datasheet SOA |

| VCE(sat) (typ) | ~1.4–2.0 V at 150–300 A | Ig = specified drive |

| Input capacitance Cies | variable, tens to low hundreds of nF | Vce, f specified |

| Qg / gate charge | moderate; design gate driver for 15–20 W switching per device | Vge range per datasheet |

| Eon / Eoff (typ) | several hundred mJ per pulse (depends on VCC, Ic, VGE) | TJ, VCC, IC per datasheet waveform |

| Recommended gate drive | Vge_on ≈ +15 V, Vge_off ≤ 0 V; include gate resistor | observe dV/dt limitations |

Explanation: These values are starting points; switching energy and thermal performance are strongly dependent on test circuits and junction temperature. Use the datasheet waveforms and stated test conditions (Tj, Vcc, If) to extract accurate Eon/Eoff and conduction loss numbers for your operating point.

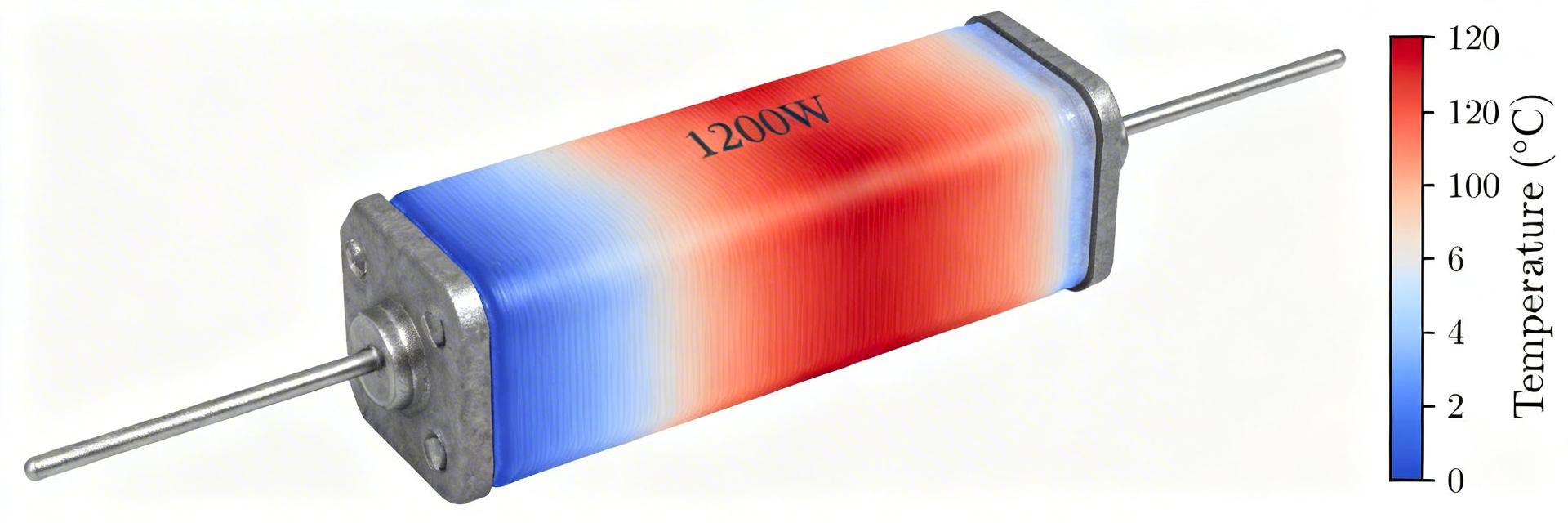

Thermal limits & mechanical ratings

Point: Thermal resistance and maximum junction/case temps set allowable continuous power. Evidence: typical module limits include Tj(max) ≈ 150°C, recommended Tc(max) for long life ≈ 100°C, and low Rth(j‑c) per IGBT chip to enable effective heat transfer. Explanation: follow recommended mounting torque, use a uniform flat interface and thermal interface material with measured interface resistance. Confirm bolt pattern and footprint against the mechanical drawing and include thermistor or temperature sensing if available in the chosen suffix.

How to read the datasheet and verify the specs (method guide: "datasheet" + "specs")

Interpreting tables vs. graphs

Point: Datasheet tables give absolute maxima and recommended operating points; graphs show performance trends and derating. Evidence: SOA plots, switching energy curves and thermal derating graphs contain the real usable limits for waveform‑dependent events. Explanation: extract usable values by reading curves at your operating Tj and current; note the test circuit used for Eon/Eoff (snubber, stray inductance) and replicate similar measurement setup when validating on the bench.

What specs matter for selection

Point: Prioritize voltage margin, continuous current rating, switching loss and thermal resistance. Evidence: practical rules: 20–30% voltage margin above DC link, 25–50% current derating depending on cooling, and derate switching energy with rising Tj. Explanation: choose the module with adequate SOA for expected short‑circuit events, and size cooling so case temperature stays within recommended Tc under worst‑case losses.

Example system design using F3L600R10N3S7FBPSA1 (case showcase)

3‑level inverter power stage example

Point: A compact three‑level inverter using this module targets a 700–900 V DC link with RMS phase currents up to 250–300 A. Evidence: choose switching frequency 2–8 kHz for traction/motor drives to balance switching and conduction losses; gate drive must supply adequate peak current to charge module input capacitance. Explanation: conduction loss estimate Pcond ≈ VCE(sat) × Iavg; for VCE(sat) = 1.6 V and Iavg = 250 A, Pcond ≈ 400 W per conducting device; include switching losses from Eon/Eoff at your Vdc and current to compute total dissipated power per module.

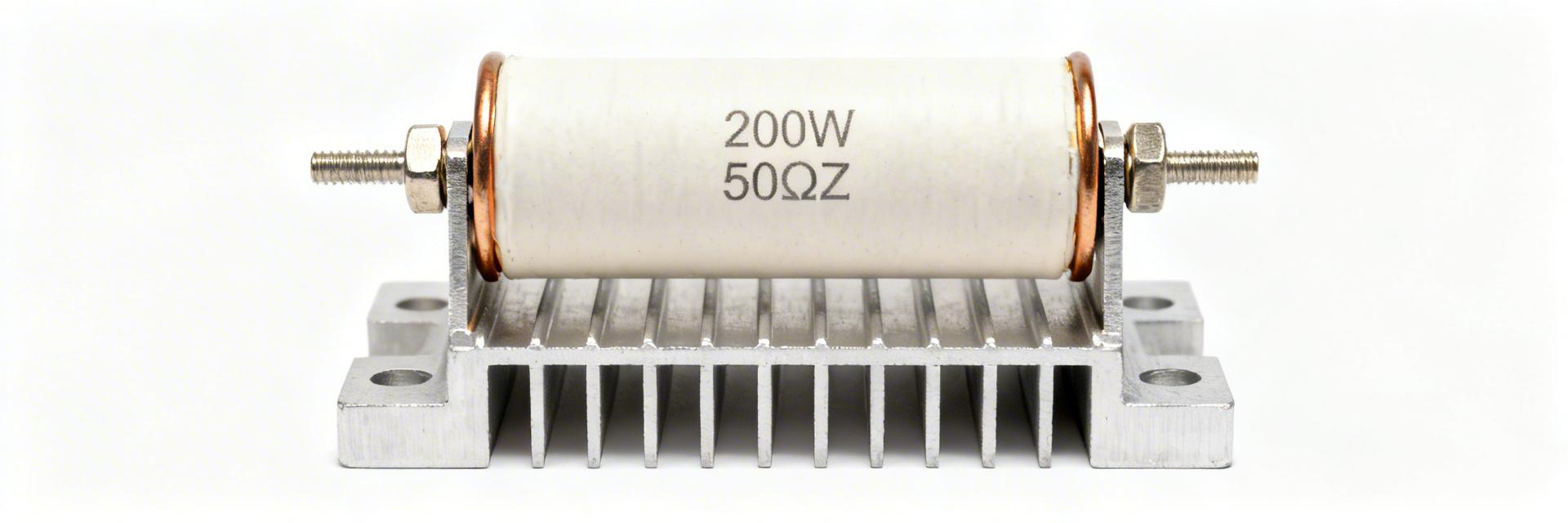

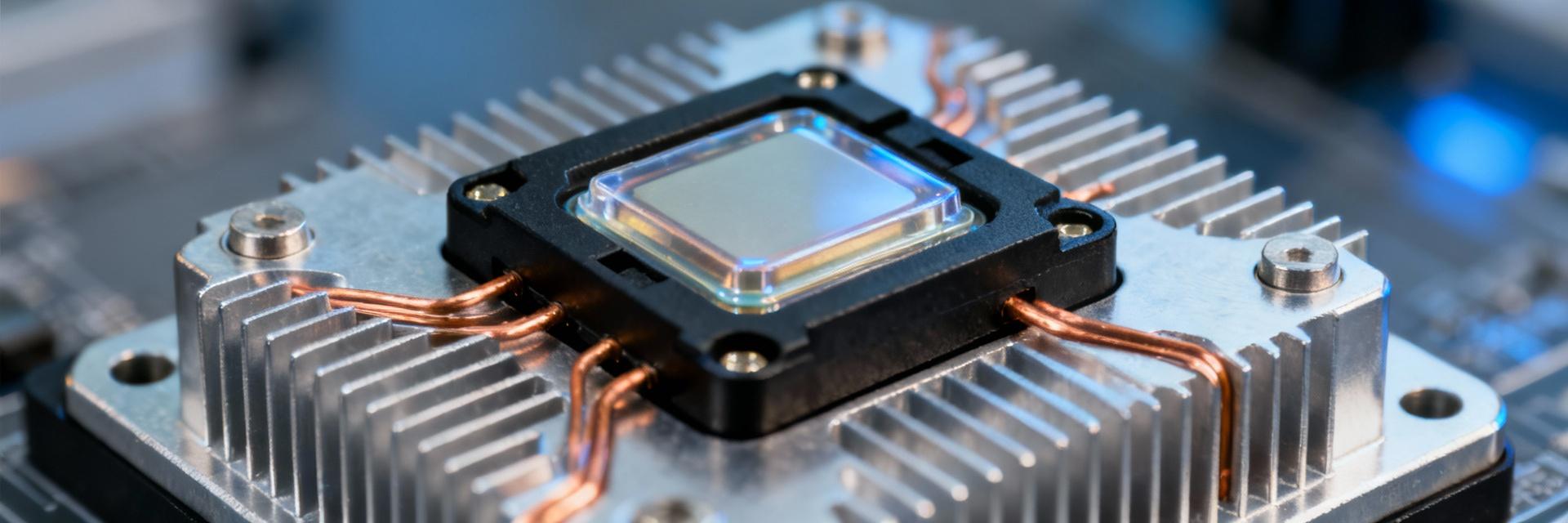

Thermal management, layout & protection tips

Point: Effective cooling and layout reduce thermal gradients and stray inductance. Evidence: use wide, short busbars or direct copper bus, minimize loop area between DC link and inverter bridge, and choose liquid cooling for sustained high power or forced‑air with large heatsinks for intermittent loads. Explanation: add desaturation detection, fast short‑circuit sensing, and temperature monitoring at the case; size heatsink so case temperature stays below the datasheet recommended Tc under worst‑case power dissipation plus a safety margin.

Design validation & deployment checklist (action suggestions)

Bench tests and key measurements

Point: Validate electrical and thermal behaviour stepwise on the bench. Evidence: core tests—insulation and continuity, gate drive verification, static VCE(sat) and leakage at defined Tj, switching loss measurement with the datasheet test circuit, thermal rise under controlled current. Explanation: run switching tests at representative Vcc and Ic, log waveforms and temperatures; pass/fail criteria should be based on staying within datasheet SOA, acceptable VCE(sat) increase and stable thermal response over test duration.

Reliability & safety verification before field deployment

Point: Accelerated and in‑system tests reduce field failures. Evidence: perform thermal cycling, humidity exposure, vibration (if applicable), and long‑run endurance at elevated case temperature. Explanation: finalize protection thresholds (desat, overcurrent, overtemperature) and set up runtime logging for case temperature, junction estimates and current spikes to enable early detection of degradation in the field.

Summary

- The module provides a high‑voltage, high‑current three‑level IGBT solution; confirm rated voltage and continuous current on the manufacturer's datasheet before system selection to ensure electrical margin and SOA compliance.

- Key specs to extract are Vce/VCEO, continuous and pulsed IC ratings, VCE(sat), gate charge, Eon/Eoff with test conditions, plus Rth(j‑c) and Tj/Tc limits; use those numbers to size cooling and gate drivers.

- Validate on the bench with the datasheet test waveforms: measure conduction and switching losses, verify thermal rise under load, exercise protection features and perform environmental stress tests prior to deployment.

Frequently asked questions

What are the most important datasheet specs to check for a high‑power inverter module?

Check blocking voltage, continuous and peak current ratings, VCE(sat) and its temperature dependence, switching energies with stated test conditions, thermal resistances Rth(j‑c), and maximum junction/case temperatures. These determine electrical margins, cooling needs and protection thresholds for reliable operation.

How should switching energy and conduction losses be validated against datasheet specs?

Replicate the datasheet test circuit (Vcc, Ic, gate drive waveform, stray inductance) and measure Eon/Eoff and VCE(sat) under the same Tj. Compute conduction losses Pcond = VCE(sat) × Iavg and combine with switching losses at intended switching frequency to size heatsinking and confirm thermal limits.

Which thermal management checks are necessary before field deployment?

Perform steady‑state thermal rise tests at maximum expected power, thermal cycling for reliability, and assess case‑to‑heatsink interface resistance. Verify that case temperature stays below recommended Tc under worst‑case load plus safety margin, and enable runtime monitoring of case/estimated junction temperature.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606