-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

FGH4L40T120RWD IGBT Specs Report — 1200V 40A Insight

Product Overview & Package Background

The FGH4L40T120RWD presents a 1200V 40A class discrete IGBT intended for industrial inverter and power-supply applications. These ratings define system voltage margins, required current-carrying capacity of collectors and emitter conductors, and gate-driver isolation/protection requirements. Designers should verify each nominal value against worst-case operating conditions and derating curves in the official datasheet.

Core Electrical Identity

Point: State core rated values so designers can quickly map device to system.

Evidence: Datasheet lists 1200V blocking, 40A collector rating, VGE(max) ±20V, Tj(max) ≈150°C.

Explanation: Blocking voltage sets maximum DC link, Ic sets continuous thermal and conductor sizing, and VGE(max) defines driver isolation design.

Mechanical & Package Implications

Point: Package drives thermal path and mounting strategy.

Evidence: Supplied in a three-lead high-power discrete package with insulated/heatsink-mount options.

Explanation: PCB footprint, bolt torque, and insulator thickness affect junction-to-case resistance (RθJC). Always follow vendor outlines for heatsink interfaces.

Key Electrical Specifications Explained

Using the derating curve to compute allowable Ic at given Ta: Ic_allowed = Ic_rated × derating_factor(Ta). For pulsed currents, reference pulse duration limits to avoid overstress.

| Parameter | Datasheet Value (Example) | Design Implication |

|---|---|---|

| Blocking Voltage | 1200V | Choose DC-link ≤ 800–900V for safety margin |

| Continuous Ic | 40A | Derate by Tcase/Ta curves for long-term reliability |

| Pulsed Current | Refer to Pulse Chart | Limit pulse width and duty cycle per SOA boundaries |

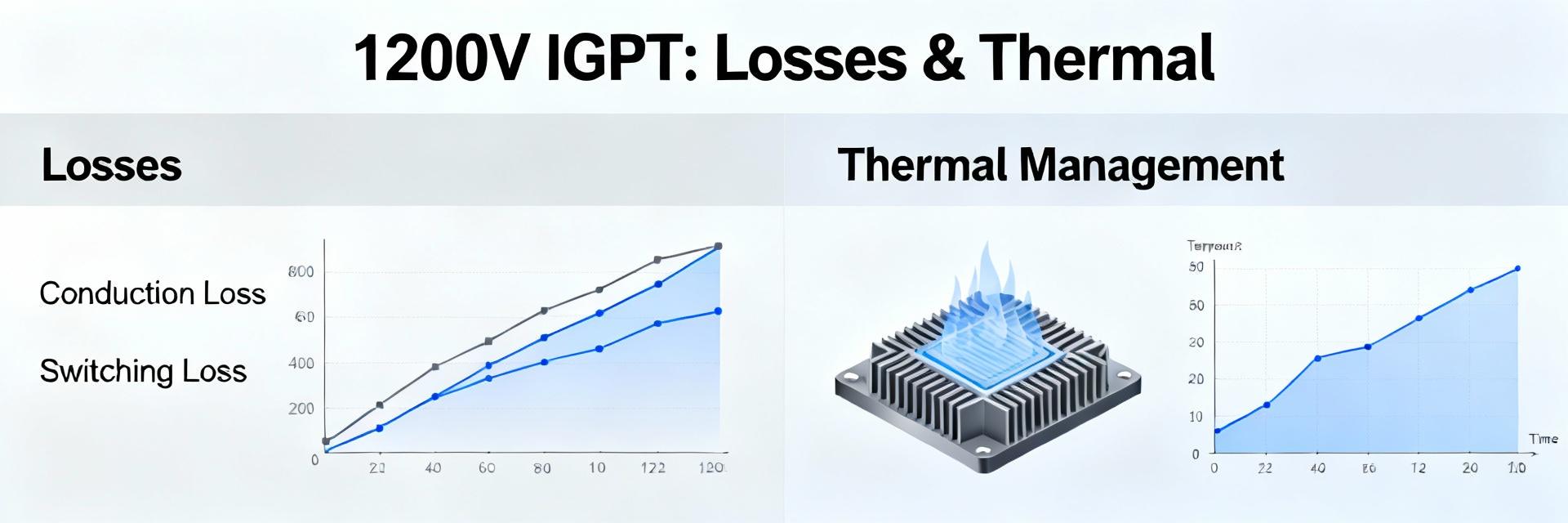

VCE(sat) Impact on Conduction Loss

Conduction loss often dominates at low switching frequencies. Pcond = VCE(sat) × Ic.

Example: with VCE(sat)=2.0V at 40A, Pcond = 80W per device. Designers should size cooling to remove this steady-state power.

Switching Performance & Dynamic Behavior

Convert per-switch energy to average switching loss: Psw = (Eon + Eoff) × fsw × duty_factor. Ensure test conditions used match your operating Vcc/Ic.

| Test Condition | Eon | Eoff | Comment |

|---|---|---|---|

| VCC=600V, Ic=20A, Rg=10Ω | Datasheet Value | Datasheet Value | Use for preliminary Psw budgeting |

Gate Drive Requirements

- Miller Charge: Qg, Qgs, Qgd shape driver current needs.

- Peak Current: Driver must source/sink Qg × Vdrive / trise.

- Ranging: Typical Rg is 5–20Ω to balance speed vs overshoot.

- Protection: Add RC damping to control ringing from parasitic inductance.

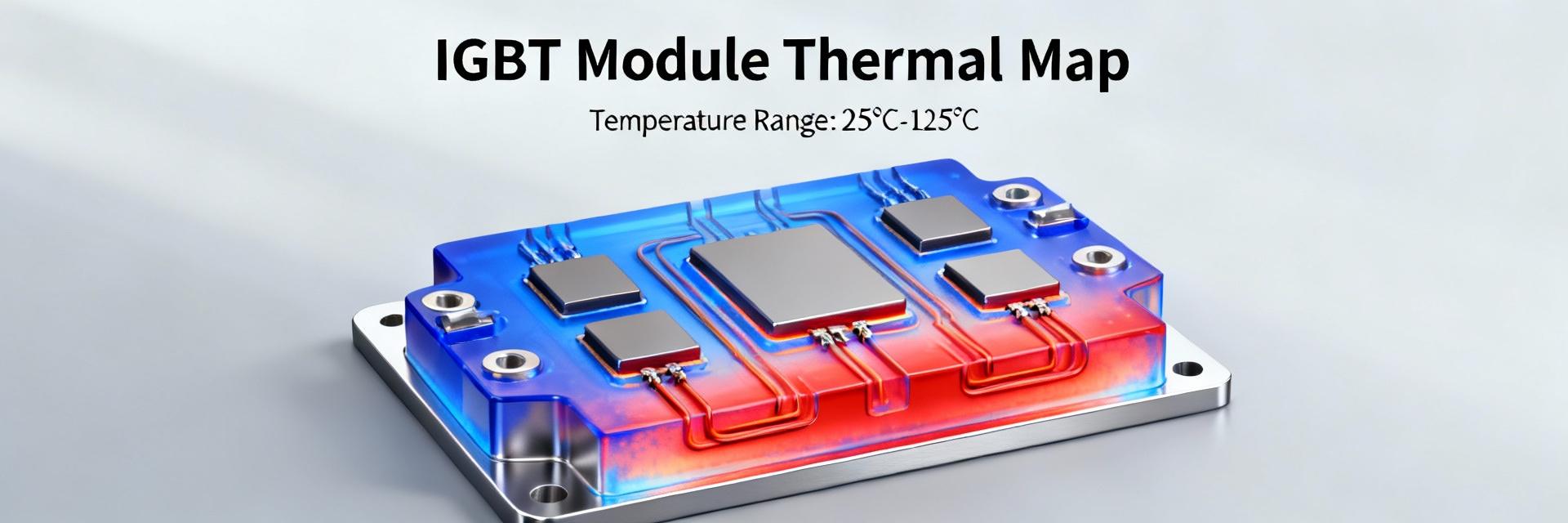

Thermal & Reliability Modeling

Steady-state Junction Temperature: Tj = Ta + Pd × RθJA (or Tj = Tc + Pd × RθJC for heatsink designs).

Adopt conservative margins (10–20°C below Tj(max)) and validate with thermal imaging under full-load conditions to ensure device survival during startup and faults.

Application Scenarios

Medium-voltage three-phase inverters.

Half-bridge configurations for light rail.

High-voltage resonant converters.

String inverters with 600-900V DC links.

Selection & Integration Checklist (FAQ)

Pre-selection Validation Checklist

- Confirm DC-link and transient margin vs 1200V rating.

- Verify continuous Ic and pulsed limits against load profiles.

- Assess thermal budget: Pd estimates and RθJC implications.

- Check gate-drive voltage and peak current vs Qg.

- Validate short-circuit duration and SOA boundaries.

- Review mechanical mounting and supply-chain risk.

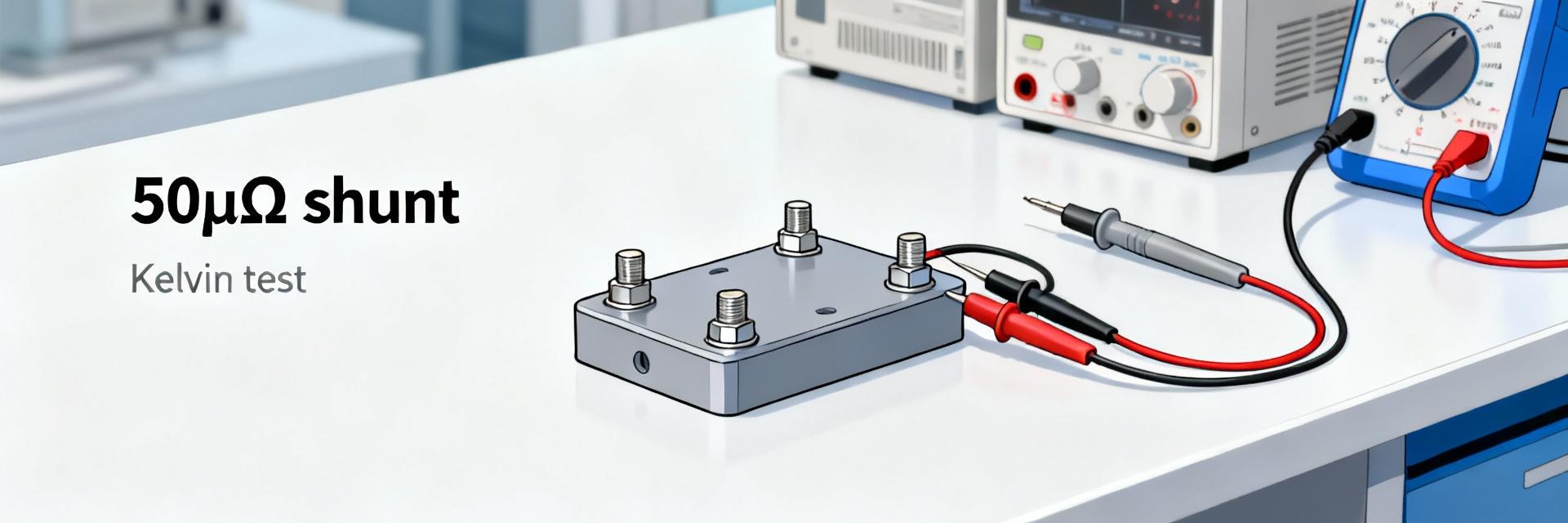

Assembly & Testing Best Practices

Bench plan should include:

- Controlled switching tests (specify VCC, Ic, Rg).

- Thermal imaging under steady-state load.

- SOA pulse testing and end-of-line checks.

- Capturing loss maps and switching waveforms for dossier.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606