IGBT Module Failure Report: Safe Test Metrics & Risk Map

Recent field audits and lab tests indicate that IGBT module failures remain a leading cause of inverter and motor-drive downtime, driven primarily by thermal stress, short-circuit events, and gate-driver faults. This report frames practical diagnostics and a prioritized response, naming critical metrics and prescribing safe test procedures for modules such as SNXH225B95H3Q2F2PG-N1.

Background — Failure Modes & Why IGBT Module Reliability Matters

Common failure modes to document

The dominant failure modes seen in high‑power IGBT modules include thermal overstress, bond-wire lift, solder fatigue, short-circuit avalanche, gate-oxide failure, and collector-emitter leakage. Field case logs correlate rising junction-to-case ΔT and solder-interface cracking with later VCE(sat) drift and intermittent opens.

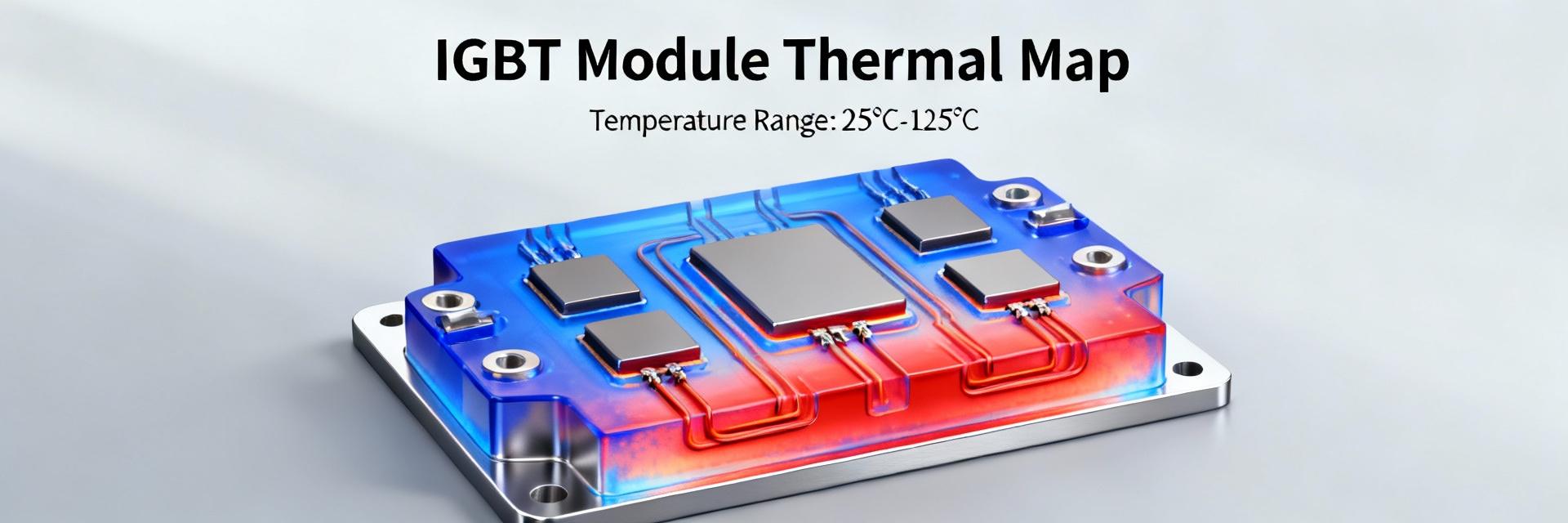

- Thermal overstress Substrate warpage measured via RthJC shifts and thermal mapping.

- Bond-wire lift Mechanical fatigue visible as intermittent opens and VCE(sat) variance.

- Solder fatigue Gradual VCE(sat) increase correlated with thermal cycling.

- Short-circuit avalanche Catastrophic energy deposition; captured as high di/dt spikes.

- Gate-oxide failure Gate leakage or threshold drift evident in DC gate tests.

- Collector-emitter leakage Elevated ICEO at temperature via leakage sweeps.

System-level impact & safety implications

Module failures propagate to system downtime and collateral hardware damage. Aggregated MTBF estimates show single-module failures can trigger replacement costs that exceed the module price by orders of magnitude.

Data Analysis — Field Test Metrics & Failure Trends

Effective diagnostics rely on technical test metrics. Trending these across population samples reveals early degradation trends.

Failure Mode KPI Visualization (Impact Weight)

Failure trends, visualization & KPIs

Visualization accelerates root-cause identification. Key KPIs include failure rate per 10,000 operating hours, median time-to-failure (MTTF), and short-circuit duration histograms. Ensure data sources include field logs and thermal-camera records for validation.

Method Guide — Safe Testing Procedures & Measurement Protocols

Pre-test safety & isolation checklist

Safety reduces test risk and preserves evidence integrity. Implement a mandatory written checklist:

- • Lockout/tagout & full discharge procedures.

- • Secure clamp-down of bus bars.

- • Required PPE (Face shield, insulated gloves).

- • Verified scope-probe grounding & instrument calibration.

Standardized test protocols

Establish pass/fail criteria by combining device datasheet limits and baseline fleet characterization:

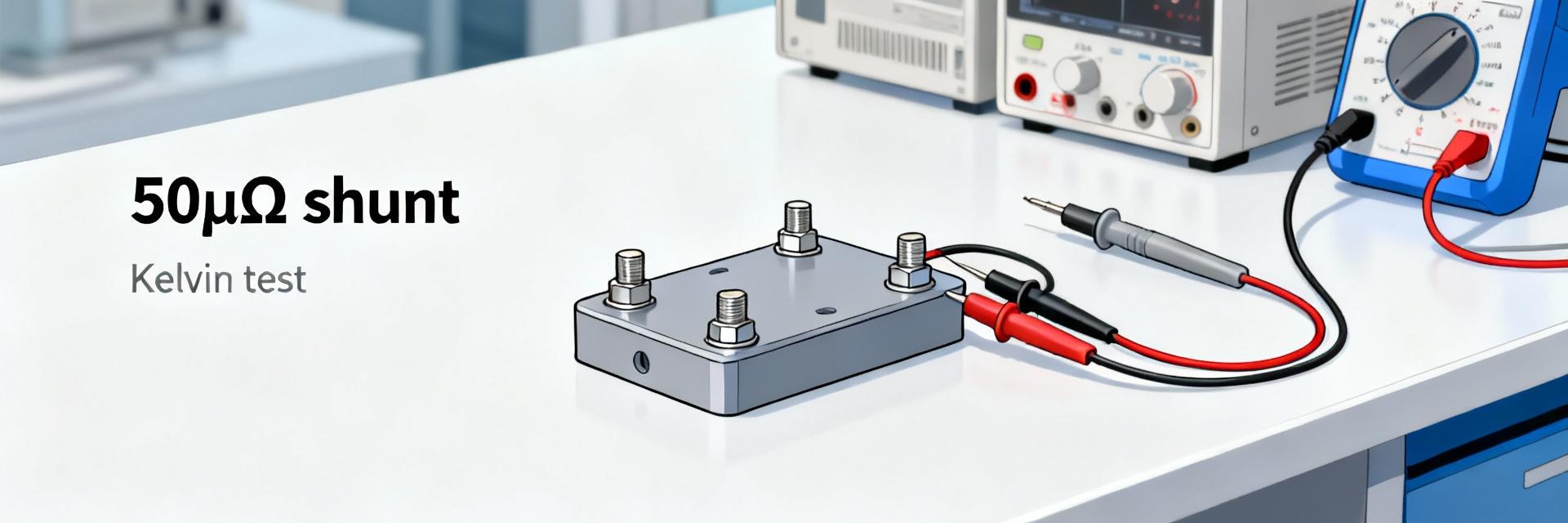

- • Static tests: Diode checks, leakage sweeps.

- • Dynamic tests: Turn-on/turn-off under load.

- • Controlled short-circuit tests with measured tSC.

- • Logged waveforms and timestamped thermal images.

Case Study — Building a Risk Map: From Failure Mode to Action

A simple scoring method translates data into prioritized actions. Failure modes are scored by frequency (likelihood) and system impact (severity).

| Failure Mode | Likelihood (1-5) | Severity (1-5) | Recommended Action |

|---|---|---|---|

| Solder fatigue | 3 | 3 | Monitor RthJC, schedule interface upgrade |

| Short‑circuit avalanche | 2 | 5 | Implement fast protection, limit tSC |

| Bond-wire lift | 4 | 4 | Redesign bonding, add current sensing |

Likelihood Scoring: 1=Rare, 5=Frequent | Severity Scoring: 1=Minor, 5=Catastrophic

Actionable Recommendations — Maintenance Playbook & Design Mitigations

Routine monitoring

Define rolling thresholds (e.g., alarm at 10% deviation). Implement condition-based maintenance tied to trend velocity rather than fixed time intervals.

Design mitigations

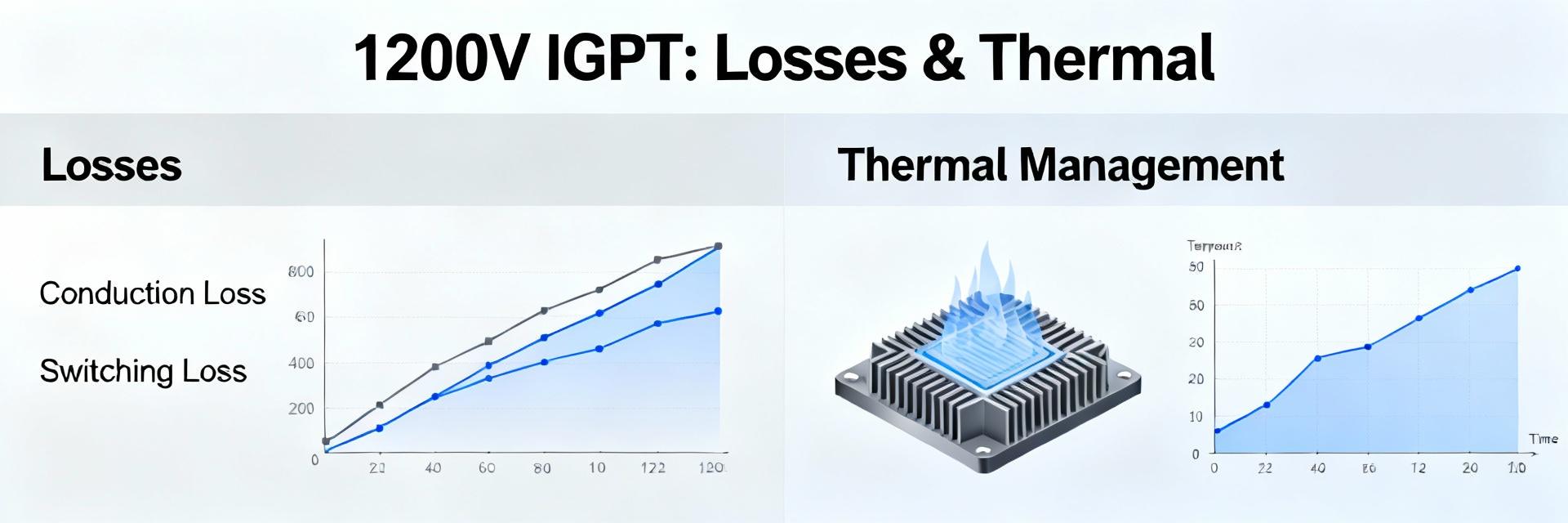

Apply derating strategies, improved heatsinking, and gate-driver desaturation detection to reduce in-service failures and optimize efficiency trade-offs.

Summary

The essential takeaway is to define and trend critical test metrics (VCE(sat), leakage, RthJC, tSC), follow safe, repeatable test protocols, and use a likelihood × severity risk map to prioritize mitigations. Engineers assessing high-performance modules should combine baseline characterization with continuous monitoring to justify design changes.

Key Takeaways

- ✓ Monitor core metrics continuously to detect early degradation.

- ✓ Adopt standardized, safety-first test protocols with traceable logging.

- ✓ Use a risk map to prioritize fixes: high-impact risks addressed first.