-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

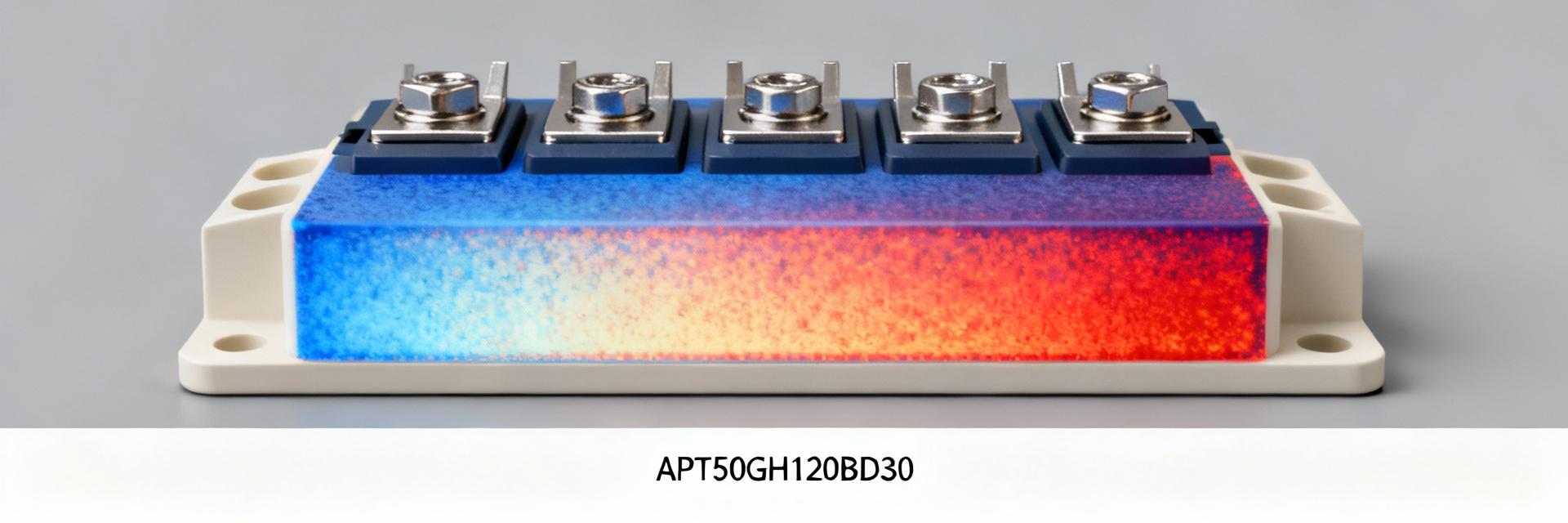

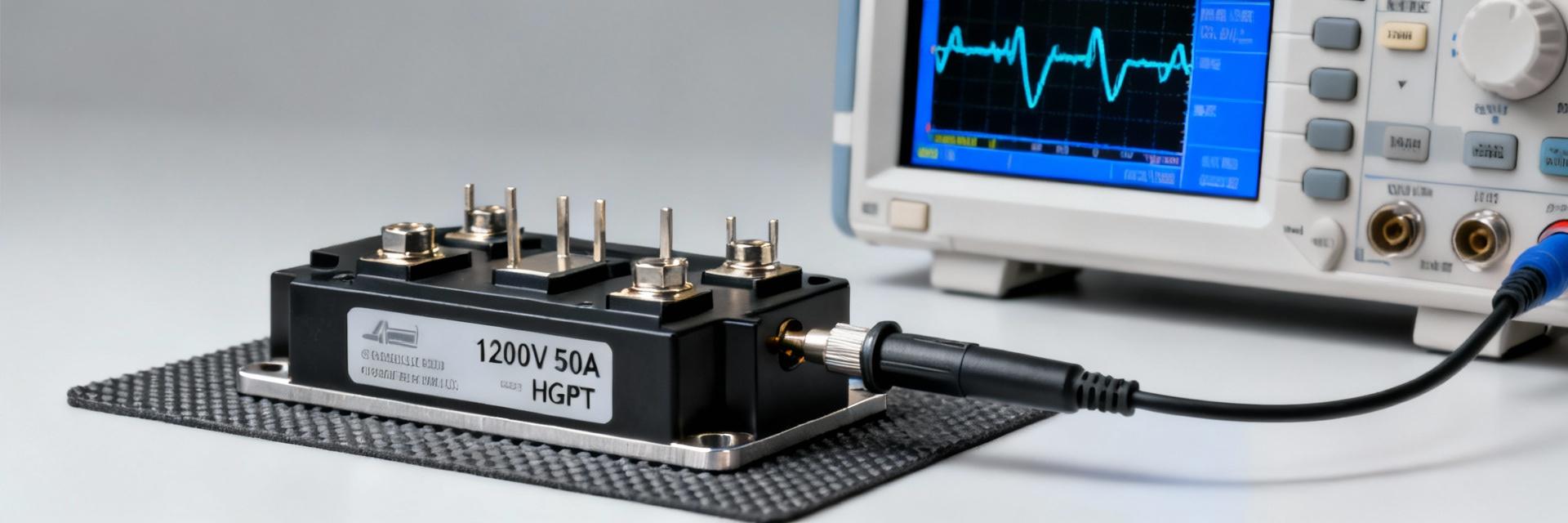

APT50GH120BSC20 Datasheet Deep Dive: Key Specs & Graphs

Introduction: Point — The APT50GH120BSC20 is specified for a 1200 V collector–emitter rating and a 50 A nominal collector current, ratings that place it squarely in medium‑power inverters, industrial converters and motor drives. Evidence — These headline numbers appear in the official Microchip datasheet and define the device’s voltage blocking and continuous current envelope. Explanation — This deep dive extracts the datasheet’s critical tables and graphs, interprets implications for conduction and switching loss budgeting, and supplies a compact design checklist for lab validation and thermal sizing.

1 — APT50GH120BSC20 Datasheet Overview & Absolute Ratings (background)

What to pull from the Absolute Maximum Ratings table

Point — Capture the absolute limits designers must never exceed: VCES, IC (continuous), IC pulse (single and repetitive), maximum junction temperature (Tj max), storage temperature and VGE max. Evidence — The datasheet’s Absolute Maximum Ratings column lists these limits and any pulse durations or waveform conditions. Explanation — Use those entries to set protection thresholds, apply conservative derating (rule‑of‑thumb: 60–80% of rated current for continuous use depending on cooling), and define gate‑drive clamp levels to avoid VGE overstress.

Pinout, package and mechanical notes to extract

Point — Copy package type, case drawing, pin numbering, thermal pad dimensions and mounting torque recommendations from the mechanical section. Evidence — The mechanical drawings and recommended PCB footprint in the datasheet specify lead spacing and suggested solder/fastener details. Explanation — Follow PCB thermal pad guidance, short current loops, and place Kelvin sense traces for the emitter to minimize stray inductance and measurement error during switching tests.

2 — Core Electrical Characteristics: DC & Static Specs (data analysis)

Key DC parameters to present and explain

Point — Present VCE(sat) (typical/max) vs IC and junction temperature, VGE(th), ICES and blocking characteristics. Evidence — The datasheet’s DC characteristics table and VCE(sat) vs IC curves provide these data points. Explanation — VCE(sat) drives conduction loss (Pd_cond = VCE(sat)×IC); use the worst‑case VCE(sat) at elevated Tj for thermal budget and choose device paralleling or heat sinking accordingly.

Long-term performance factors: temperature coefficients & leakage behavior

Point — Account for temperature dependence: VCE(sat) usually increases with junction temperature while leakage current rises exponentially. Evidence — Characteristic graphs and notes in the datasheet illustrate VCE(sat) vs Tj and ICES vs Tj. Explanation — Thermal design must assume higher conduction losses and larger standby leakage at elevated ambient; include margin in heatsink sizing and enable idle‑mode protections when the converter is offline.

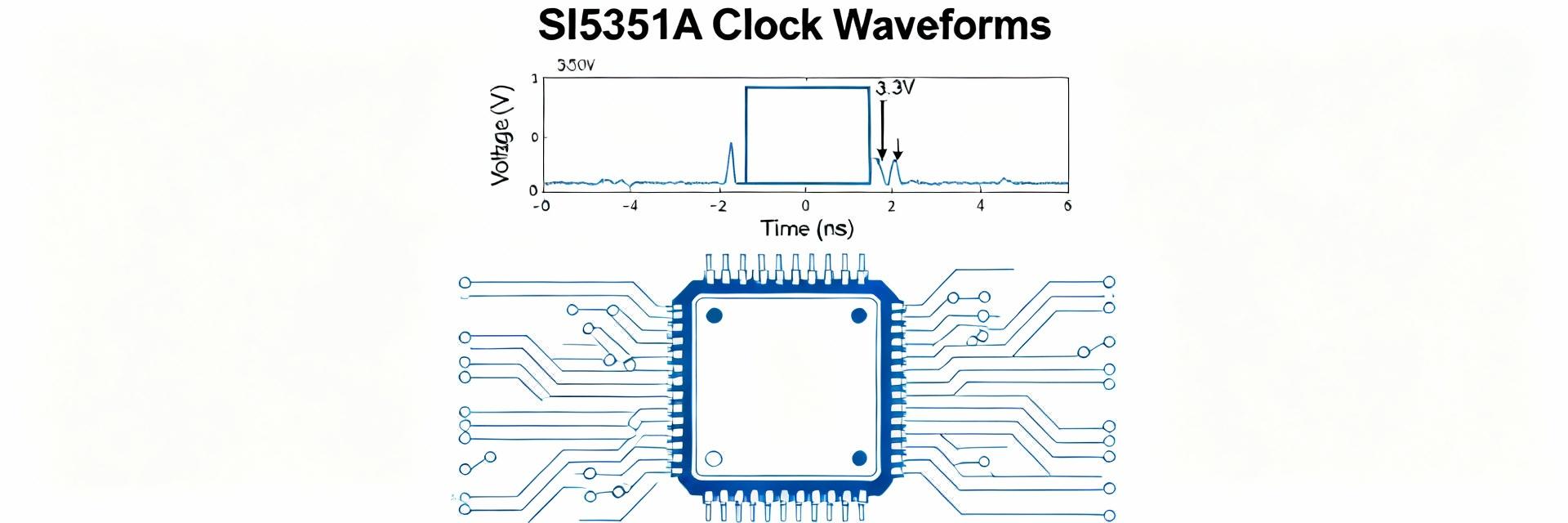

3 — Dynamic Performance & Switching Graphs (data analysis / graphs)

Which datasheet graphs to reproduce + how to interpret them

Point — Recreate Turn‑on/Turn‑off waveforms, Eon/Eoff vs IC or VCE, di/dt & dv/dt limits, and gate charge/Qg profiles. Evidence — Each graph in the switching section includes axes labels, test conditions and gate drive values. Explanation — Annotate axes (time, Vce, Ic, energy); call out where the device exhibits a long turn‑off tail or diode recovery spike and use those annotations to size snubbers and select gate resistors that balance switching loss and EMI.

Switching-energy to loss budgeting workflow

Point — Calculate switching loss as Pswitch = (Eon + Eoff) × fSW × margin. Evidence — Datasheet Eon/Eoff curves provide energy per event vs current or voltage; use the listed test conditions or mark examples as illustrative if test conditions differ. Explanation — For example (illustrative only), with Eon=0.12 J and Eoff=0.18 J at a given Ic, at 10 kHz Pswitch ≈ (0.30 J)×10,000 = 3,000 W per device before margins — clearly showing why realistic Eon/Eoff values and tail energy matter for system thermal design.

4 — Thermal Behavior, SOA & Reliability Considerations (method guide)

Thermal impedance and mounting recommendations

Point — Extract RthJC (and RthCH if present) and follow recommended mounting to achieve datasheet thermal performance. Evidence — The thermal section lists RthJC and recommended torque/insulator/grease notes. Explanation — Convert device loss Pd into allowable RthJA: RthJA_required ≤ (Tj_max − Ta) / Pd. Step‑by‑step: estimate Pd, pick Ta, solve for RthJA, then choose heatsink or cooling to meet that limit with margin.

Safe Operating Area (SOA) and pulsed limits

Point — Read DC, pulsed and repetitive SOA plots to verify allowable VCE vs IC for given pulse durations and temperatures. Evidence — SOA figures map current vs voltage for multiple pulse widths and for different junction temperatures. Explanation — For inductive switching, follow the time‑dependent SOA lines, avoid intersecting the DC line during avalanche or hard switching, and apply derating for elevated Tj and repetitive duty cycles.

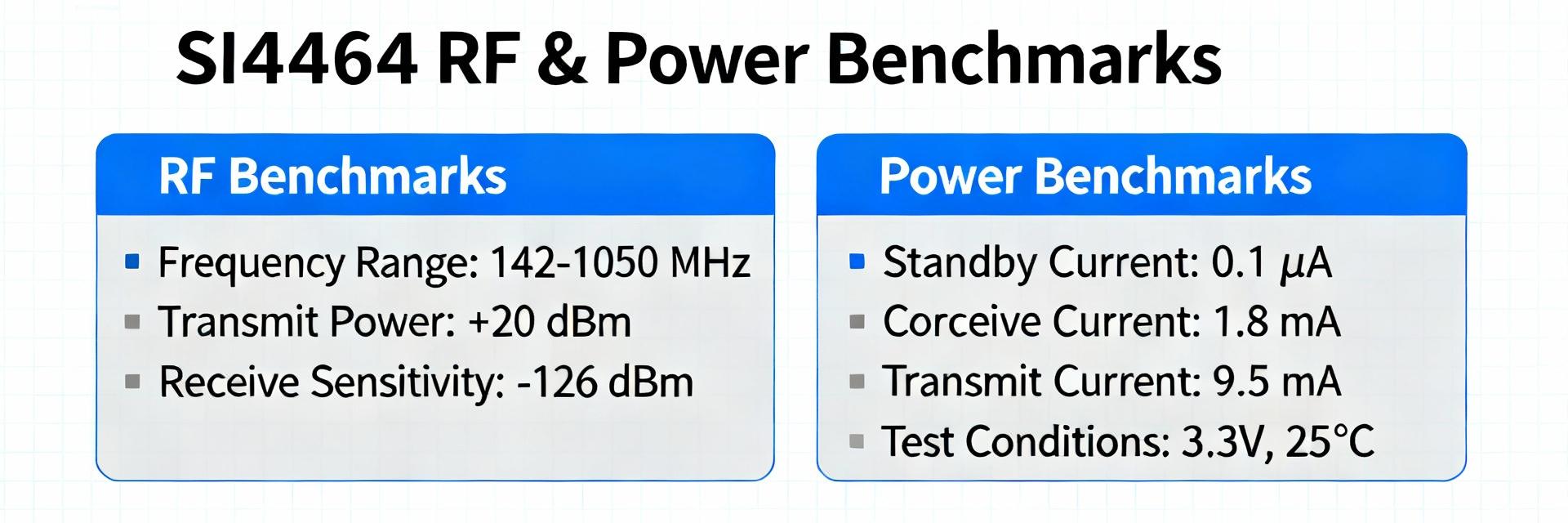

5 — Benchmarks & Alternatives: How APT50GH120BSC20 Compares (case)

Direct datasheet comparison checklist

Point — Compare columns: VCE(sat), Eon/Eoff, RthJC, SOA limit lines, and anti‑parallel diode recovery characteristics. Evidence — A compact table with parameter, this part’s value and competitors’ entries makes selection decisions straightforward. Explanation — Use that table to spot tradeoffs: lower VCE(sat) reduces conduction loss; softer diode recovery reduces EMI but can raise switching loss.

When to choose APT50GH120BSC20 vs alternatives

Point — Select this part for high‑voltage motor drives needing Field‑Stop behavior and robust SOA; choose alternatives when lower VCE(sat) or different diode recovery is prioritized. Evidence — Matching application profiles to datasheet strengths (switching energy, thermal impedance) guides selection. Explanation — If your topology emphasizes hard switching at high voltage with tight thermal control, the part’s 1200 V/50 A rating and switching profile can be a strong fit.

6 — Practical Design Checklist & Application Tips (action)

Quick pre-layout checklist for engineers

- Gate drive: set VGE clamp, choose Rg to balance dV/dt and loss.

- Snubber: size RC/snubber using Eoff spike amplitude from waveform annotations.

- Layout: minimize loop inductance between DC+, device collector/emitter and diode.

- Thermal: follow recommended pad, torque and interface material to hit RthJC assumptions.

Test and validation plan using datasheet graphs

Point — Reproduce key datasheet plots in lab: DC VCE(sat) vs IC, turn‑on/off waveforms, thermal ramp and SOA pulses. Evidence — Use the same Vdc, Ic, gate voltages and probe points noted in the datasheet test conditions where possible. Explanation — Typical probe points: measure Vce across the device, Ic via low‑resistance shunt, and gate waveform at the driver output; run thermal ramp tests to validate RthJC assumptions and incremental SOA pulsed stress to confirm robustness.

Summary

Point — The APT50GH120BSC20 is a 1200V 50A Field‑Stop IGBT family member whose datasheet provides the DC, switching and thermal graphs needed to size conduction and switching losses, design heatsinks, and validate SOA. Evidence — Headline ratings and the suite of tables/plots in the datasheet form the engineering basis for selection. Explanation — Top takeaways: (1) use datasheet Eon/Eoff and gate‑profile graphs for switching loss budgeting; (2) follow thermal mounting guidance and compute RthJA targets from Pd; (3) validate SOA with pulsed tests under realistic thermal conditions. Next steps: download the official datasheet, extract the precise test conditions, and run the bench validation sequence described above.

Key Summary

- Use headline ratings (1200 V, 50 A) as selection floor and apply 60–80% derating for continuous operation depending on cooling and ambient.

- Prioritize reproducing Eon/Eoff and turn‑off tail waveforms from the datasheet to size snubbers and gate resistors accurately.

- Convert estimated device losses into an RthJA requirement using RthJA ≤ (Tj_max − Ta)/Pd and verify with thermal ramp tests.

常见问题解答

What are the critical absolute limits I should extract from the datasheet?

Extract VCES, continuous IC, single‑pulse IC, maximum junction temperature, storage temperature and VGE max. These set protection thresholds and determine derating; use the datasheet’s specified pulse durations when interpreting pulse current limits.

How do I use datasheet Eon/Eoff curves to estimate switching losses?

Read Eon and Eoff at your target Ic and VCE test points, then compute Pswitch = (Eon+Eoff)×fSW with a safety margin. Ensure the datasheet’s test conditions match your operating point or label numerical examples as illustrative if they differ.

What lab probes and conditions reproduce datasheet switching graphs?

Probe VCE across the device with a low‑capacitance high‑voltage probe, measure Ic with a Kelvin‑connected shunt, and record gate voltage at the driver output. Match Vdc, gate amplitude and load current to the datasheet test conditions for valid comparison.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606