-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

TDP16035002AUF Datasheet: Precision Specs & Metrics

The following data-driven summary highlights the precision metrics that matter most to analog designers: number of resistors, package type, typical tolerance, channel-to-channel matching, temperature coefficient, ratio drift, and operating temperature range. These metrics determine gain error, offset drift, and long-term stability in precision instrumentation and ADC front-ends. This introduction sets expectations for interpreting a datasheet and planning verification and integration steps using clear electrical and mechanical criteria.

Key terms used in this article include datasheet and precision specs, with focused coverage on resistor network characteristics, thin-film resistor behavior, and resistor array considerations relevant to precision analog designs in the US market.

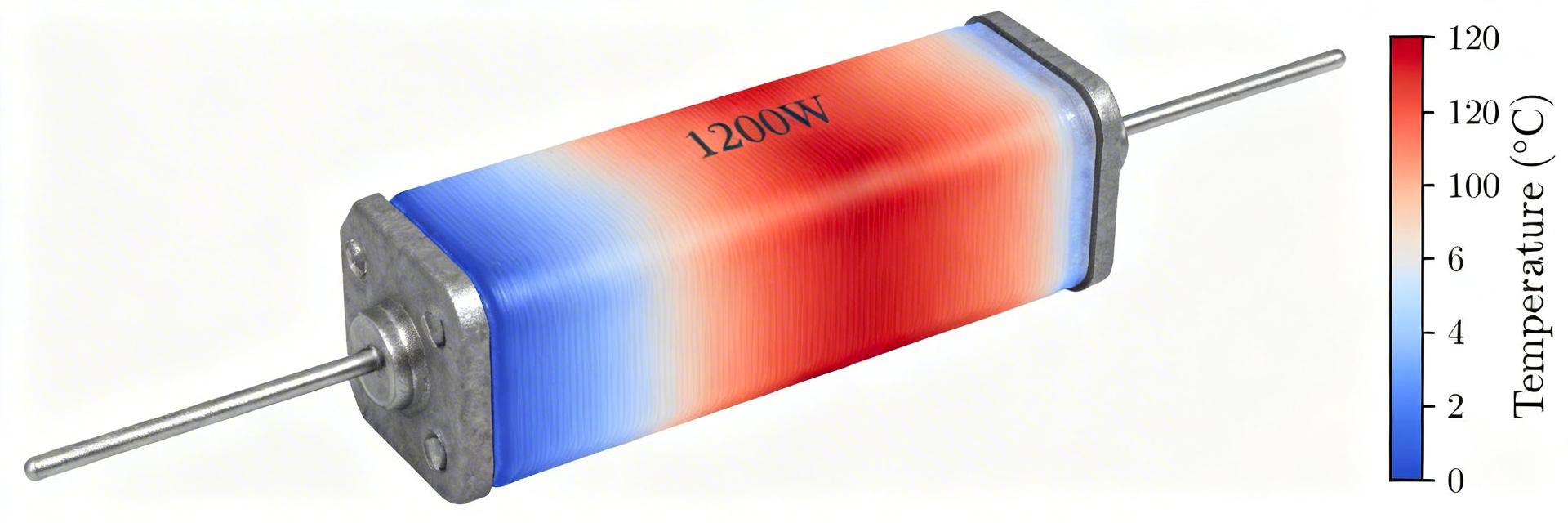

At-a-glance technical overview — TDP16035002AUF key specs (background)

Quick technical summary (one-table snapshot)

The table below presents a compact specification snapshot to use as a hero reference when evaluating the part for board-level designs. Confirm exact test conditions in the official datasheet before design-in.

| Parameter | Value (typ / max) |

|---|---|

| Part type | Precision thin-film resistor network |

| Number of resistors | 4 elements |

| Nominal resistances | 10 kΩ, 100 kΩ options |

| Tolerance | ±0.1% typ / ±0.5% max |

| Channel-to-channel matching | ±0.02% typ / ±0.05% max |

| Ratio drift | ≤ 2 ppm/°C typ |

| Temperature coefficient (TCR) | 5 ppm/°C typ |

| Package | 8-pin SMD, gull-wing |

| Operating temp range | -55°C to +125°C |

| Power rating per element | 125 mW at 70°C derated |

Intended applications and product fit

Resistor networks like this target precision instrumentation, sensor front-ends, ADC input networks, and bridge circuits. Tight resistor matching reduces differential gain error, low TCR limits temperature-induced offset, and small ratio drift preserves calibration over environmental swings. Use cases include low-noise instrumentation amplifiers, high-resolution ADC inputs, and low-drift Wheatstone bridges where cumulative mismatch drives measurement error.

Electrical characteristics & precision metrics from the datasheet (data analysis)

Resistance values, tolerance, and channel-to-channel matching

Nominal resistance options are typically offered in standard E24/E96 values; tolerance and channel matching are separate specs. Typical tolerance may be ±0.1% with worst-case ±0.5%. Channel-to-channel matching of ±0.02% typical (±0.05% max) governs differential error. Test conditions are usually 25°C and a specified measurement current—confirm these before acceptance testing.

Example calculation: a differential amplifier with resistor pair matched at ±0.05% yields a gain error ≈ 0.0005 (0.05%). For a nominal gain of 100, that mismatch causes ~0.05 gain error, directly impacting LSB accuracy on a 24-bit ADC. Design margin should allocate additional budget for tolerance, drift, and measurement uncertainty.

Temperature coefficient, stability, and long‑term drift

TCR given in ppm/°C converts to relative resistance change: ΔR/R = TCR × ΔT. For 5 ppm/°C over a 100°C swing, change is 500 ppm (0.05%). Ratio drift often specified separately (e.g., 2 ppm/°C) and is the critical figure for matched elements. Long-term drift may be stated in ppm/year—plan for worst-case cumulative change over product lifetime and include calibration intervals if needed.

| Spec | ΔR/R over -55°C→125°C |

|---|---|

| TCR 5 ppm/°C | ~0.4% (4000 ppm) |

| Ratio drift 2 ppm/°C | ~0.16% (1600 ppm) |

Mechanical, packaging, and thermal limits (data analysis)

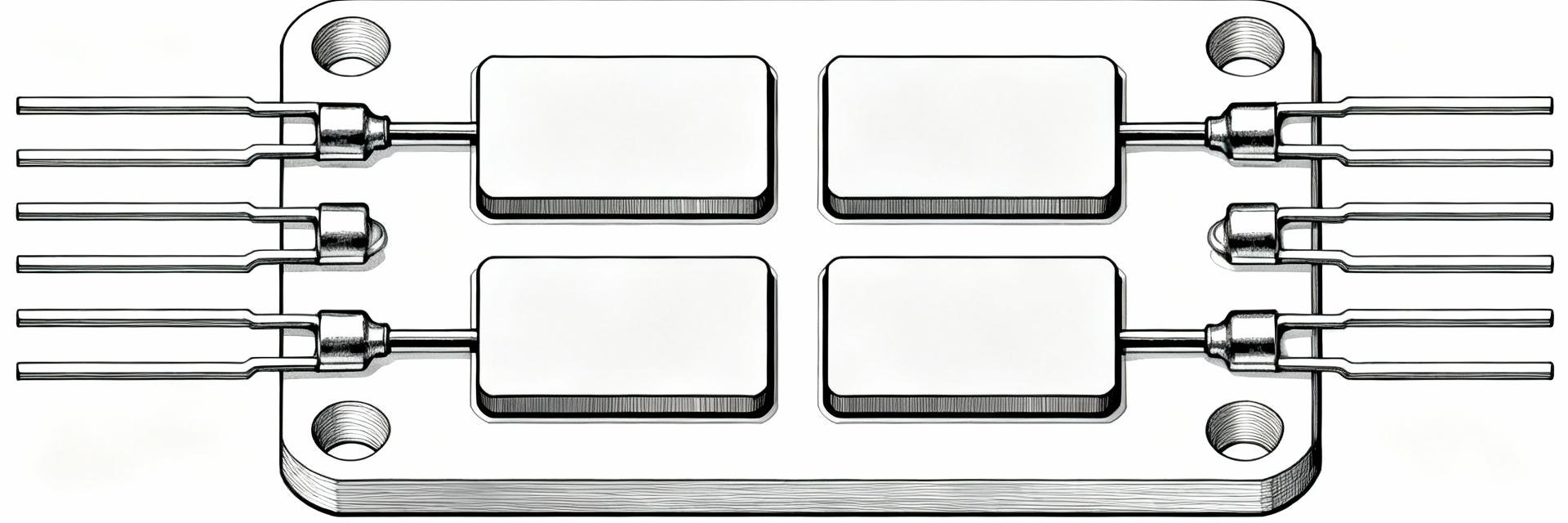

Package, pinout, and footprint guidance

Package is an 8-pin SMD with standard gull-wing leads. Confirm exact outline dimension block for pad land pattern. Recommended PCB footprint uses solder fillets sized to manufacturer-recommended land pads; maintain equal trace lengths for matched resistors and provide thermal symmetry. Keepout zones under the package reduce thermal conduction differences between elements.

Power rating, derating, and thermal performance

Per-element power rating commonly 125 mW at 70°C, derated to zero at maximum temperature. Use a linear derating curve: full power at 70°C, 50% at 100°C, zero at 175°C as a conservative example. Thermal resistance and ambient mounting affect self‑heating; rule of thumb: limit continuous dissipation to 50% of rated power for high-precision circuits to avoid thermally induced matching shifts.

How to read, interpret, and verify datasheet numbers (method guide)

Interpreting “typical” vs “maximum” and test-condition callouts

“Typical” indicates median or common performance; “maximum” is guaranteed under specified test conditions. Always check the test temperature, applied current, and measurement method. Red flags include unspecified test conditions, ambiguous units, or missing ratio-drift spec. Checklist: note test temp, measurement current, sample size, and qualification method before design-in.

Recommended bench verification protocol for precision specs

Verification equipment: precision DMM (0.1 ppm resolution desirable), stable current source, temperature chamber or hotplate. Steps: measure tolerance at 25°C, measure channel-to-channel matching under identical excitation, run temperature sweep to derive TCR and ratio drift, and record long-term stability if possible. Suggested sample size: 10 units per lot with statistical checks (mean, sigma). Pass/fail thresholds should be set tighter than datasheet max to allow margin for system error.

Case study — bench comparison and integration metrics (case)

Example bench test results & data visualization

Hypothetical results: measured tolerance mean ±0.09% (spec ±0.1%), matching mean ±0.018% with 3σ = 0.04% (spec max ±0.05%). A histogram of channel-to-channel variation and resistance-vs-temperature plots expose outliers and slope. Replicate graphs: histogram of ΔR/R, resistance vs temperature line fits, and a derating curve overlay to visualize safe operating regions.

When channel-to-channel matching or ratio drift dictates design choices

Scenario A: high-resolution ADC front-end—prioritize matching and low ratio drift to limit gain error; choose networks with ≤0.02% matching. Scenario B: Wheatstone bridge—matching dominates offset; prefer networks with low ratio drift and thermal symmetry. Quantify impact by converting ppm drift into equivalent voltage offset at expected bridge excitation.

Selection checklist & integration tips for engineers (action)

Pre‑selection & procurement checklist

Before ordering: confirm exact resistance option, tolerance and matching specs, package and pinout, operating temperature range, per-element power rating, and availability/supply considerations. Order samples across production lots to evaluate lot-to-lot variation; request characterization data from the vendor if available. Verify part marking and MOQ to align with QA sampling plans.

PCB layout, de‑rating, and assembly tips for preserving precision

Layout tips: route matched traces symmetrically and keep lengths equal; avoid routing high-power traces adjacent to resistor arrays; place thermally active components away from the network. For SMD parts, follow recommended reflow profiles and post-reflow cleaning that avoids flux residue under packages. Include test pads for in-circuit trimming or calibration and reserve space for shunt resistors if needed for calibration.

Summary

- Nominal resistances and tolerance: choose the value that minimizes excitation current while keeping tolerance and matching within system error budget; tight tolerances reduce initial calibration needs.

- Channel-to-channel matching and ratio drift: these determine differential gain and temperature-induced offset; prioritize low ppm/°C ratio drift for precision ADCs and bridges.

- Thermal and power considerations: derate per-element power conservatively, maintain thermal symmetry on the PCB, and limit self-heating to preserve matching and long-term stability.

- Verification and procurement: run a bench protocol with a precision DMM and temperature sweep, sample multiple lots, and require vendor test conditions before full production sign-off.

- Integration tips: use symmetrical routing, test pads for calibration, and conservative derating rules to maintain long-term precision.

Final note: consult the TDP16035002AUF datasheet — precision specs as the authoritative source for guaranteed limits and test conditions when finalizing component selection and validation plans.

Frequently Asked Questions

How does the TDP16035002AUF matching specification affect ADC front-end accuracy?

Channel-to-channel matching directly determines differential gain error in ADC front-ends. A ±0.05% matching limit can introduce proportional gain error; lower matching (±0.02% or better) reduces this source of error. Designers should budget matching error into total system error and consider calibration if necessary.

What test conditions are recommended to verify the datasheet tolerance and temperature coefficient?

Verify tolerance at 25°C with a stable current source and precision DMM. For TCR, perform a controlled temperature sweep (e.g., -55°C to +125°C) in a chamber and record resistance at multiple points to fit ppm/°C. Ensure measurement uncertainty is smaller than the spec you intend to verify.

When should I prioritize resistor array matching over nominal tolerance in selection?

Prioritize matching when differential accuracy or ratio stability drives system performance—examples include instrumentation amplifiers and bridge sensors. If the application is single-ended or can be recalibrated frequently, nominal tolerance may be sufficient; otherwise, choose networks with tighter matching and lower ratio drift.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606