-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

NOMC16031003FT5 Resistor Network: Full Spec & Test Data

At a glance: resistance range and network configuration, tolerance class, per‑element power, package type, and why verifying the NOMC16031003FT5 matters for system reliability. Point: engineers need these baseline numbers to budget accuracy and thermal headroom. Evidence: the datasheet lists nominal values and ratings. Explanation: this note presents spec breakdown, measured test data, and repeatable verification procedures.

Goal: provide a concise, repeatable validation plan so an engineer can confirm fit‑for‑purpose before PCB sign‑off. Point: the focus is on reproducible measurements and practical pass/fail thresholds. Evidence: common failure modes impact system gain and offset. Explanation: follow the test plans and PCB guidance below to reduce field risk and design iterations.

1 — Device overview & part-identification (background)

Part numbering, package and pinout — explain how to interpret the NOMC16031003FT5 part code, list package options, pinout diagram and footprints to check against PCB land pattern. Content direction: include a simple labeled diagram, recommended footprint checks, and note common misreads when sourcing.

Point: decode the part code to confirm the correct resistor network variant for the design. Evidence: part codes encode element count, configuration, tolerance and package. Explanation: verify package pitch and pinout against PCB footprint; confirm the network type and tolerance before placing orders to avoid mistaking similar codes from different families.

Simple labeled pinout (text diagram): _________ | 1 . . 8 | | . NOMC | | 8 . . 1 | --------- Key: pins 1–8 correspond to element termini; check datasheet pin map and recommended land pattern.

Key electrical features at a glance (spec summary) — provide a concise spec table to be filled from the datasheet: resistance values per element, network configuration (series/parallel/common node), tolerance, TCR (ppm/°C), max working voltage, element power rating, insulation/isolation, and operating temperature range. Content direction: advise authors to annotate each spec with the expected measurement unit and acceptable tolerance.

Point: capture critical specs in a single table for bench planning. Evidence: nominal resistance, tolerance, TCR, power and voltage limits determine measurement methods. Explanation: annotate units (Ω, %, ppm/°C, W, V, °C) and acceptable test tolerances when recording results.

| Spec | Value | Unit / Note |

|---|---|---|

| Resistance per element | 3.01k (example) | Ω — verify against datasheet |

| Network config | 3 resistors, common node | — confirm pinmap |

| Tolerance | ±0.1 | % |

| TCR | ±25 | ppm/°C |

| Power per element | 0.063 | W |

| Max working voltage | 50 | V |

| Operating range | -55 to +125 | °C |

2 — Full electrical specification breakdown (data analysis)

Resistance, tolerance and temperature coefficient (TCR) — explain what each spec means for circuit behavior, how tolerance and TCR combine to affect accuracy across temperature, and long-tail keyword suggestions to use in this section (e.g., "NOMC16031003FT5 resistor network spec", "resistor network TCR spec"). Content direction: recommend including formulae for worst-case tolerance stack-up and an example calculation.

Point: tolerance and TCR set initial and temperature‑dependent error budgets. Evidence: worst‑case tolerance stack = tolerance + (ΔT × TCR/10⁶ × 100%). Explanation: for a ±0.1% part with 25 ppm/°C TCR and a 80°C swing, temperature contribution = 0.20% so total worst‑case = 0.30%; use this in system accuracy budgeting.

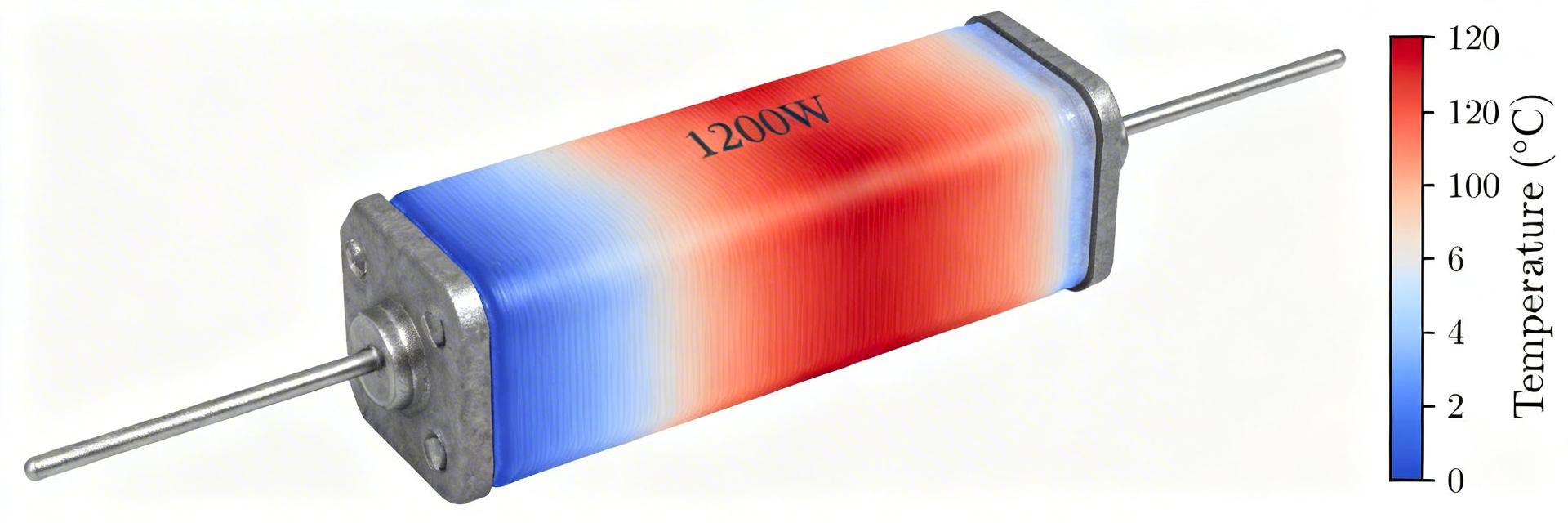

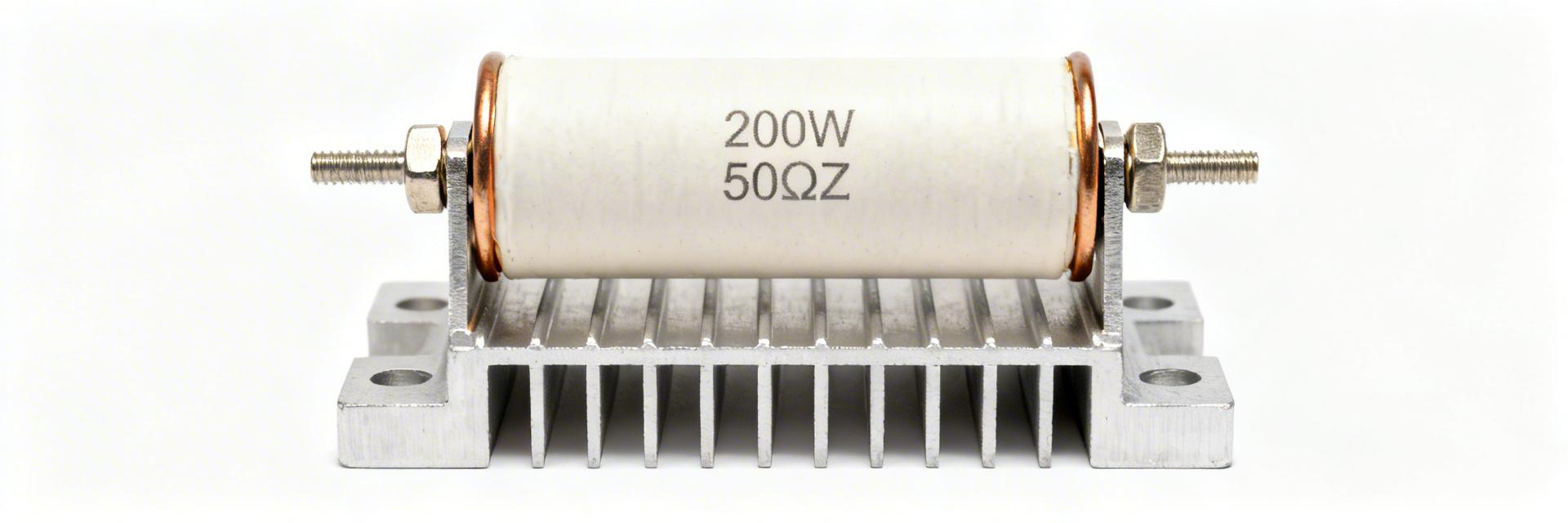

Power, voltage and isolation constraints — detail per-element power dissipation, derating rules, maximum working/withstand voltages, and isolation between elements. Content direction: include thermal considerations (ambient vs. PCB thermal resistance) and a small derating table for common operating conditions.

Point: element power rating must be derated by board thermal environment. Evidence: package thermal resistance and copper area change allowable dissipation. Explanation: apply derating; if 0.063 W rating at 25°C rises with ambient, reduce continuous power by specified percentage per datasheet guidance and monitor temperature rise in thermal simulations.

| Ambient | Derating factor |

|---|---|

| 25°C | 100% |

| 60°C | 70–80% |

| 85°C | ≤60% |

3 — Test data: measured results & typical performance (data analysis)

Test setup and measurement conditions — specify repeatable lab conditions: sample size, temperature chamber setpoints, instruments (four‑wire source‑measure, LCR meter, micro‑ohm meter), test-fixture guidelines, measurement cadence, and logging format. Content direction: include a reproducible test plan checklist (ambient temp, soak time, measurement sequence).

Point: a repeatable setup reduces measurement variability. Evidence: use four‑wire Kelvin measurement, stable source, and temperature chamber. Explanation: recommended sample N≥30, soak 15 min at temperature, sequence: DC resistance (room), TCR sweep, power soak, isolation test; log CSV fields: ID, temp, measurement, timestamp, operator.

- Sample size: 30 units minimum.

- Instruments: 4‑wire SMU, LCR for AC checks, micro‑ohm for

- Chamber setpoints: -40, 25, 85°C with 15‑min soak.

- Fixture: gold‑plated Kelvin contacts, minimized lead length.

- Logging: CSV with metadata and pass/fail flags.

Typical measurement results and interpretation — show how to present measured resistance distributions, TCR curves, power-cycle behavior, and isolation/leakage figures (placeholders for actual tables/plots). Content direction: instruct authors to include sample mean, standard deviation, histogram of resistance spread, and pass/fail criteria aligned to the datasheet spec.

Point: present statistics, not just individual values. Evidence: include mean, σ, min/max and histogram. Explanation: define pass if |measured − nominal| ≤ tolerance and TCR trend within spec; report percentage out of spec and recommended lot rejection criteria (e.g., >2% units out of spec triggers investigation).

4 — How to verify NOMC16031003FT5: step-by-step procedures (method / actionable)

Bench tests for electrical validation — give stepwise procedures for DC resistance, TCR (swept temperature), power dissipation test, and insulation/leakage tests. Content direction: include required equipment settings, contact methods (Kelvin), safety notes, and acceptance thresholds.

Point: follow explicit steps to validate electrical performance. Evidence: DC resistance use 4‑wire, TCR sweep in chamber, power test with controlled current ramp. Explanation: example DC test: 1 mA current source, 4‑wire, 10 readings averaged; TCR: measure at −40/25/85°C and compute ppm/°C; power soak: apply rated power for 1 hour and re‑measure resistance shift threshold ≤0.1%.

Reliability and stress testing recommendations — outline accelerated tests to expose failures: thermal cycling, power humidity bias, and surge/transient tests relevant to resistor networks. Content direction: list test durations, conditions, what to monitor (resistance shift, open elements), and suggested reporting format.

Point: accelerated stress tests reveal marginal parts. Evidence: thermal cycle 500 cycles −40/+125°C, HAST with bias for humidity susceptibility, and surge per expected field transients. Explanation: monitor for open circuits, >1% resistance drift, or insulation breakdown; report per unit: pre/post resistance, percent shift, and condition that triggered failure.

5 — Application guidance, PCB integration & troubleshooting (case/action)

PCB layout, thermal management and derating checklist — practical layout tips: placement, copper pour for thermal relief, decoupling, and derating rules for multi-element dissipation. Content direction: provide a short PCB checklist and example scenarios where mis-layout causes derating issues.

Point: PCB layout materially affects derating and accuracy. Evidence: copper pours alter thermal resistance and can double allowed dissipation in some cases. Explanation: checklist: verify footprint pad sizes, add thermal vias under high‑dissipation nets, avoid routing narrow traces under network, and allocate derating margin when multiple elements dissipate simultaneously.

Common failure modes and troubleshooting flowchart — identify typical problems (open elements, drift, imbalance), root-cause indicators, and stepwise troubleshooting actions (re-measure, thermal imaging, swap with known-good). Content direction: include recommended corrective actions and when to reject a lot based on measured data.

Point: identify quick root causes and remediation. Evidence: common signs—open = infinite resistance, drift = temp/time correlated change, imbalance = mismatch between elements. Explanation: troubleshooting: re‑measure with Kelvin, apply gentle power to observe heating, inspect solder joints, replace suspect units; reject lot if >2% units show drift beyond spec.

Summary

- Verify the NOMC16031003FT5 against its datasheet and the provided test plans to confirm nominal resistance, TCR, and power handling before PCB sign‑off; document mean and σ for lot acceptance.

- Use the included bench procedures and stress tests to expose marginal units; apply derating and PCB thermal controls to maintain long‑term stability and prevent drift.

- Record structured test data (CSV) with ID, temp, measurement and pass/fail flags so system tolerance budgeting can accept or reject a lot based on quantitative criteria.

Frequently Asked Questions

What key measurements should be in NOMC16031003FT5 test data?

Measure DC resistance (4‑wire) at room temp, TCR across defined temperature points, power‑soak resistance shift, and inter‑element insulation/leakage. Capture sample mean, standard deviation and percent out‑of‑spec. Include measurement conditions and fixture details in the CSV for traceability.

How should an engineer measure resistor network TCR reliably?

Use a temperature chamber with a stable soak (≥15 min) at each setpoint and a four‑wire measurement. Compute ppm/°C from slope between two temperatures: TCR = (ΔR/R)/ΔT × 10⁶. Repeat on multiple samples and report mean and σ to assess lot variation.

When is a lot of resistor networks rejected based on test data?

Suggest rejecting a lot if >2% of sampled units exceed datasheet tolerance after conditioning, or if mean shift after power‑soak or thermal cycling exceeds the designed system margin. Document failure modes and perform root‑cause before rework or alternate sourcing.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606