-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

TOMC16031000FT5 Resistor Array: Failure Rates & Specs

Point: Aggregate test-lab data and field-return logs show surface-mount networks have widely varying in-service outcomes depending on thermal stress, soldering profile, and end-use environment.

Evidence & explanation: The TOMC16031000FT5 appears in many low-profile assemblies; reviewing its published specs and cross-checking internal test logs helps correlate observed failures with specific electrical and mechanical stressors. This article uses measured-failure reasoning, datasheet-reading guidance, and practical test steps to reduce field returns. It mentions the key term TOMC16031000FT5 once, and references the resistor array and specs in the opening analysis.

1 — Background: What the TOMC16031000FT5 Is and Where It’s Used

Key specs at a glance

Point: Present concise, actionable spec items so engineers can immediately compare parts.

Evidence & explanation: A compact listing format that engineers use is: Resistance per element — (e.g., 10 kΩ); Tolerance — (e.g., ±1%); Elements — (4 discrete resistors); Pin count — (8 pins). Package note: the numeric token in the type often maps to package size and land pattern guidance. To extract reliability-relevant data, list power-per-element, TCR, max working voltage, and the recommended land pattern next to the basic resistance/tolerance line for quick decision-making.

Typical applications & failure exposure

Point: Knowing where the part is used focuses failure-mode expectations.

Evidence & explanation: Common uses include pull-ups/pull-downs, input termination, resistor networks in signal conditioning, and compact bias networks. In such roles the typical stressors are steady-state power dissipation, repetitive thermal cycling, and occasional ESD or surge events. For products exposed to elevated ambient temperatures, vibration, or humidity, the network’s packaged construction and inter-element layout influence solder joint stress and in-service drift risk.

2 — Failure Rates & Field Reliability Data

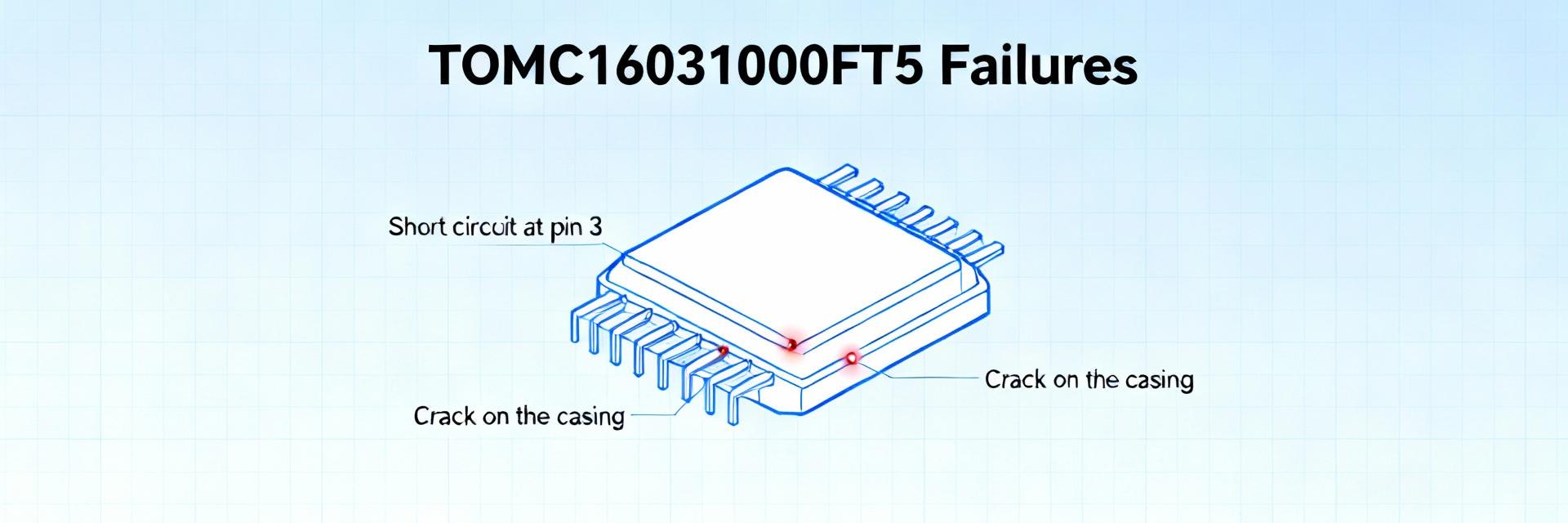

Reported failure modes and observed rates

Point: Surface-mount resistor networks commonly fail in a few repeatable ways.

Evidence & explanation: Observed failure modes include open circuits from cracked elements or leads, progressive resistance drift due to thin-film degradation, thermal-induced shifts when power is pushed near package limits, and solder-joint fractures from poor pad design or excessive mechanical stress. When reading aggregated supplier returns, bias toward in-house failure-mode詳細 logs and batch-level reflow records, since global datasets often mix stress types and conceal root-cause trends.

Root causes and contributing factors

Point: Separate process, design, and environment to trace failure trends.

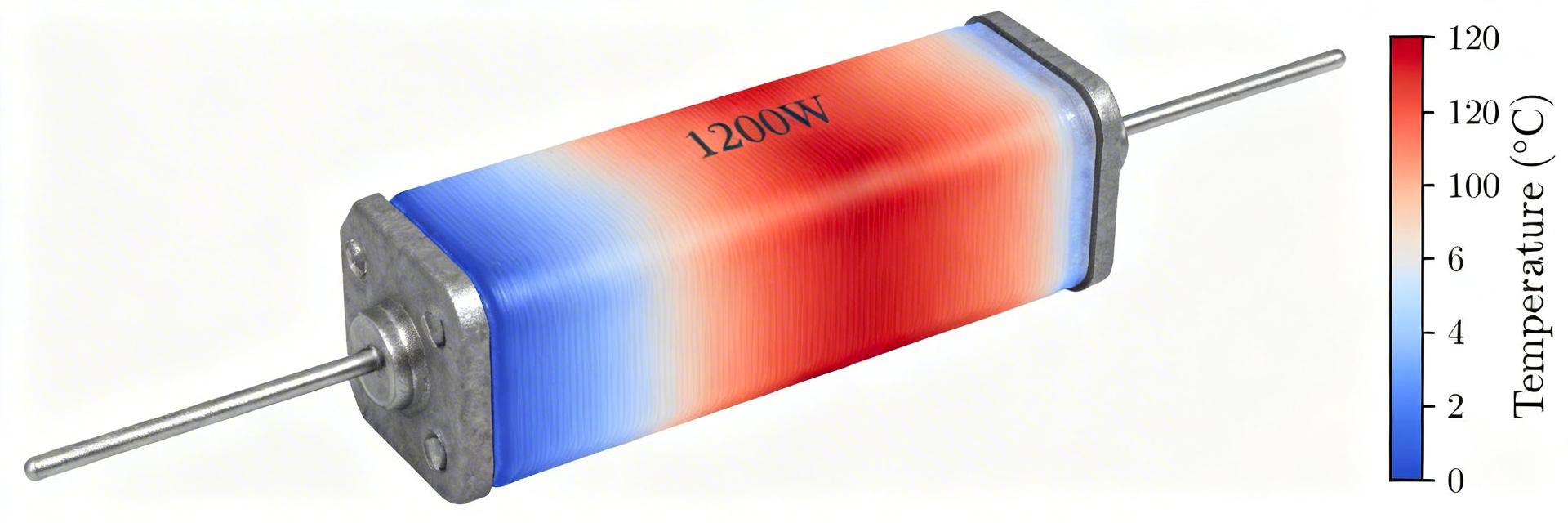

Evidence & explanation: Process causes—incorrect reflow peak and soak profiles or incompatible paste chemistry—raise solder fatigue and element stress. Design causes—insufficient derating, uneven current sharing across elements, or exceeding max working voltage—create localized overheating that accelerates drift. Environmental causes—thermal cycling amplitude, humidity with bias, and mechanical shock—produce both electrochemical and mechanical failure modes. Each factor shifts failure-rate curves: e.g., raising peak reflow 20–40°C above recommended can increase early solder-joint opens by an order of magnitude in some logs.

3 — Detailed Specs: How to Read the Datasheet for Reliability Insights

Electrical specs that matter for reliability

Point: A few electrical figures determine long-term behavior more than the nominal resistance value.

Evidence & explanation: Pull these fields from the datasheet: nominal resistance and tolerance; TCR (ppm/°C); maximum working voltage per element; rated power per element and package thermal limit; and insulation/resistance between elements if present. For derating, apply a rule: operate at ≤50–70% of rated power per element in continuous duty to limit thermal migration. The label TOMC16031000FT5 should be cross-checked against these figures to confirm the part meets margin targets before placement.

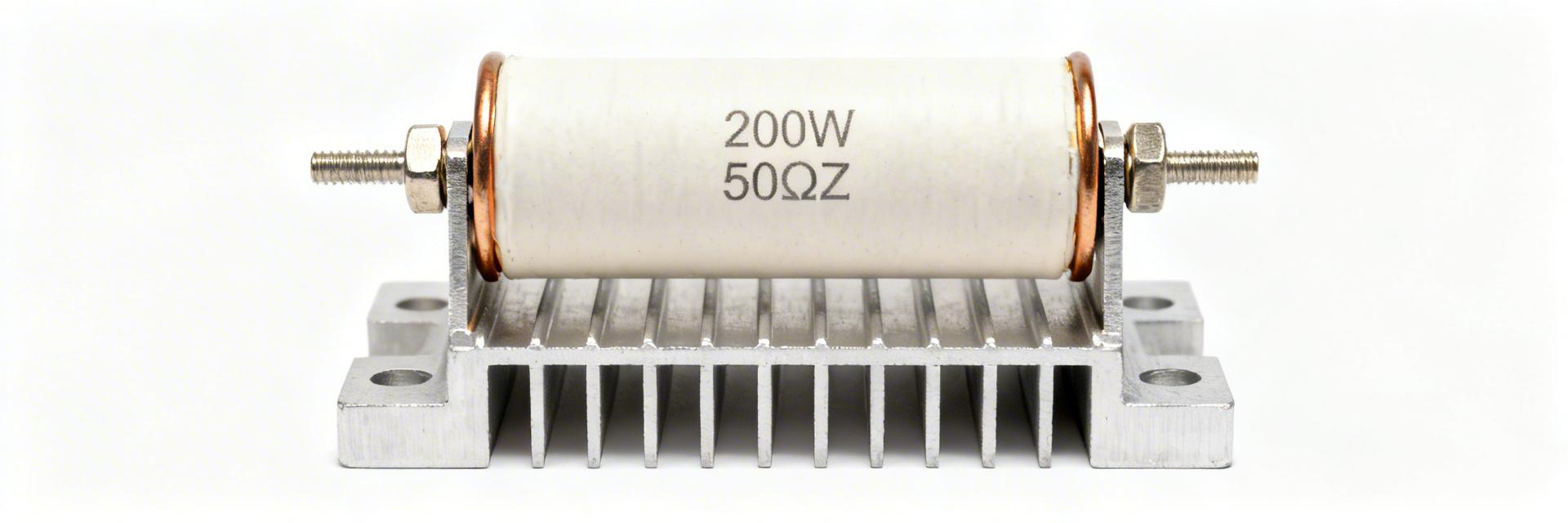

Mechanical & environmental specs to check

Point: Mechanical and shelf/environmental data translate directly to PCB and assembly requirements.

Evidence & explanation: Verify package thermal resistance and recommended land pattern, solderability statements, shock and vibration ratings, and moisture sensitivity level (MSL). Translate those numbers to actions: choose a land pattern that minimizes copper asymmetry, specify pre-bake or MSL handling when required, and ensure assembly reflow ramps respect the package’s allowable mechanical stress to reduce solder fatigue and element micro-cracking.

4 — Testing & Diagnostic Methods to Quantify Failure Risk

In-circuit and bench tests for field validation

Point: Simple bench checks quickly identify drift and open trends before full system integration.

Evidence & explanation: Recommended checks include continuity and resistance measurement against baseline tolerance, time-at-temperature soak with periodic resistance logging to detect drift, and transient surge tests replicating application-level events. Log expected baseline, pass/fail thresholds (example: >2× tolerance or >100 ppm drift over 1,000 hours triggers reject), and record the reflow profile for correlation to solder-joint issues.

Accelerated life tests and data interpretation

Point: Use standardized accelerated tests but interpret extrapolation cautiously.

Evidence & explanation: Run thermal cycling, HTOL (high-temperature operating life), and humidity-bias tests with sufficient sample sizes (e.g., 77–125 units per lot for initial assessments). Apply Arrhenius for temperature-related failures and Coffin–Manson for mechanical fatigue to extrapolate field-life, but include confidence intervals and note that mixed-mode failures (electrical + mechanical) reduce the predictive accuracy of single-model extrapolations.

5 — Replacement Options, Design Mitigations & Action Checklist

Cross-reference and replacement selection tips

Point: When substituting, match more than resistance and package.

Evidence & explanation: Prioritize tolerance, TCR, power-per-element, package thermal resistance, and MSL over mere pin compatibility. Choose substitutes with higher derating margin and lower thermal resistance if thermal stress or long life is required. Record cross-reference rationale (e.g., +20% power derating, same TCR class) to support qualification records and future root-cause analysis.

PCB, assembly and system-level mitigations

Point: Small layout and process changes dramatically reduce solder fatigue and drift.

Evidence & explanation: Use symmetric copper on pads, include thermal reliefs to avoid one-sided heatsinking, adopt conservative reflow profiles with controlled ramp rates, and add in-circuit monitoring (sense resistors or periodic self-tests) where feasible. Action checklist items: pre-production soak tests, lot-level HTOL sampling, assembly QA waveform capture, and in-service telemetry where drift can be logged and flagged.

Summary

Point: Reliability is the product of matching part capabilities to stressors, derating appropriately, and validating with targeted tests.

Evidence & explanation: The TOMC16031000FT5 performs well when its electrical and mechanical specs are respected, when soldering and land-pattern guidance are followed, and when designers apply derating and accelerated testing. Use the procedural checks and mitigation checklist above to reduce failure rates and predict field-life more accurately.

Key Summary

- Match the resistor array electrical specs—resistance, tolerance, TCR, max working voltage, and power per element—to application derating targets to avoid thermal-induced drift.

- Control process and layout: symmetric land patterns, proper reflow profiles, and compatible solder paste reduce solder-joint fatigue and open-circuit failures in compact networks.

- Validate with both in-circuit baseline logging and accelerated life tests; use Arrhenius/Coffin–Manson extrapolations cautiously and maintain conservative confidence intervals for field-life estimates.

Frequently Asked Questions

How can an engineer quickly judge TOMC16031000FT5 suitability for a high-temperature application?

Check the datasheet’s rated power per element, TCR, and package thermal resistance; apply a conservative derating (operate at ≤70% rated power) and run a short-duration thermal soak with resistance logging to reveal early drift trends before committing to production.

What are the most common failure indicators for a resistor array in signal conditioning?

Open circuits, progressive resistance drift beyond tolerance, and intermittent connections from solder fatigue are the most common. Monitor for gradual offset changes in conditioned signals and compare against baseline noise and gain to detect early signs.

Which assembly controls reduce field failure rates for compact resistor networks?

Use controlled reflow profiles with moderate peak temperatures, symmetric copper land patterns to avoid thermal gradients, compatible solder paste chemistry, and MSL-compliant handling. Add lot-level HTOL and sample reflow-record retention to correlate returns to process parameters.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606