-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

SI53306-B-GMR Datasheet Breakdown: Key Specs & Pinout

The SI53306-B-GMR supports input frequencies up to 725 MHz and provides a 1:4 fanout, numbers that immediately define its role in high-speed clock distribution and protocol fanout tasks. This article gives a practical, datasheet-driven breakdown of the SI53306-B-GMR’s key specifications, pinout, and implementation guidance so engineers can evaluate and integrate the part quickly. The goal is to make the datasheet actionable: identify the exact tables and figures to check, suggest layout and termination practices, and provide troubleshooting steps for a robust first-pass PCB bring-up.

This write-up references datasheet figure and table identifiers for cross-checking and annotates the most relevant implementation points. It targets FPGA and SerDes designers, system integrators, and hardware engineers who need concise, testable guidance to move from datasheet to working board.

1 — Background: What the SI53306-B-GMR Is and When to Use It

Overview & family context

Point: The SI53306-B-GMR belongs to the Si5330x family of any‑format clock buffers and is positioned as a compact 1:4 fanout buffer for multi-protocol distribution. Evidence: See the Si5330x family overview and device selection table in the datasheet (refer to the "Device Family Overview" table and "Ordering Options" figure). Explanation: The Si5330x family spans single- and multi-output parts with selectable output formats; the SI53306-B-GMR specifically provides four outputs (OUT0–OUT3) that can be configured as CML, HCSL, LVDS, LVPECL, or LVCMOS depending on VDDIO and strap/mode settings. Typical supply domains include core VDD (≈1.8–3.3 V range in many family members) and VDDIO for output voltage compatibility; consult the "Recommended Operating Conditions" table in the datasheet for the exact supply range for SI53306-B-GMR. This device is ideal where one clean clock source needs four matched outputs with low additive jitter and low skew.

Typical applications & system roles

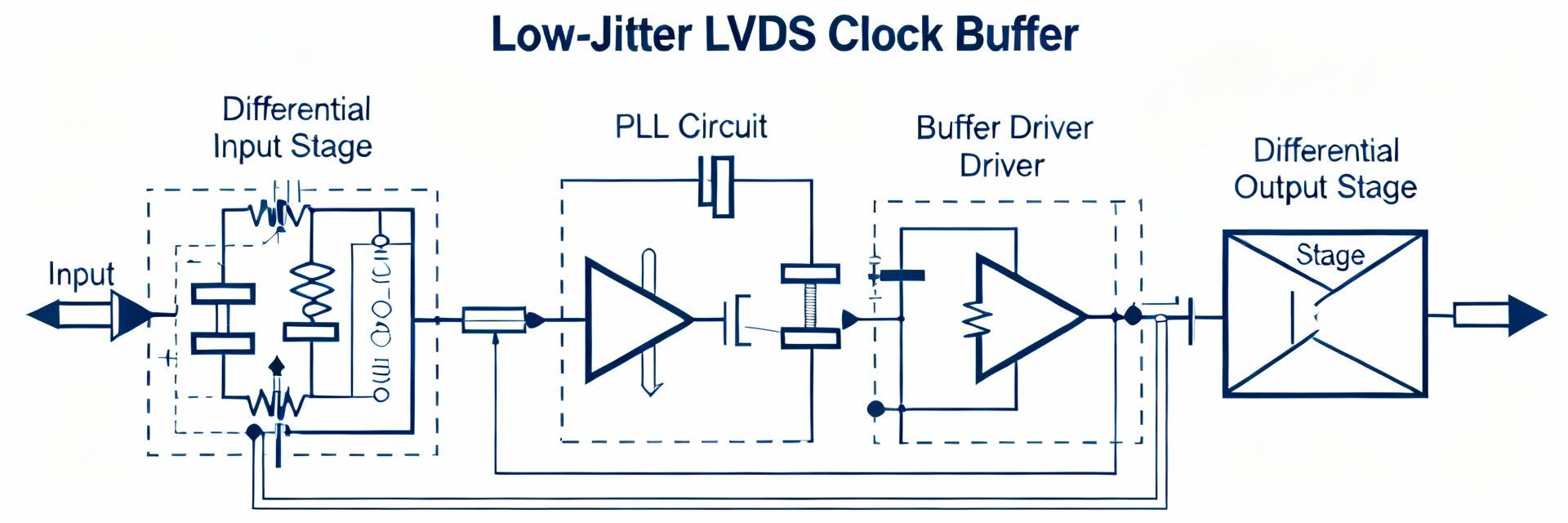

Point: The SI53306-B-GMR is used where deterministic, low-jitter clock distribution is required. Evidence: See the "Applications" section in the datasheet and application notes that list FPGA clocking, SerDes deskew, ADC/DAC front ends, and network timing. Explanation: In FPGA clock distribution, the device provides multiple outputs with selectable voltage formats to match different FPGA banks or SerDes transceivers; low additive jitter preserves link margin for high-speed transceivers. For SerDes deskew and multi-protocol links, format flexibility (CML/HCSL/LVDS) allows direct interfacing to receivers without external translators. In data-acquisition and mixed-signal systems, low jitter and matched propagation help maintain SNR and sampling timing. In switching and routing hardware, the 1:4 fanout simplifies clock tree design and reduces the need for multiple off-board sources.

Key selling points pulled from the datasheet

Point: The datasheet lists a set of headline specs that determine suitability for high-speed systems. Evidence: Refer to the "Electrical Specifications" summary table and the "Absolute Maximum Ratings" and "Recommended Operating Conditions" tables. Explanation: Key items to note: maximum input frequency: 725 MHz (datasheet "Input Clock Characteristics" table); supply range: check the "Recommended Operating Conditions" table—typical device operation spans approximately 1.71–3.63 V for combined domains depending on VDD and VDDIO selections; operating temperature: industrial range (–40 to +85 °C) as given in the "Thermal and Reliability" section; low additive RMS jitter and low output-to-output skew are listed in the "Phase Noise and Jitter" and "Timing" tables. These figures are what make the SI53306-B-GMR attractive for preserving SERDES margins and tight clock trees.

2 — Key Electrical & Performance Specs (datasheet deep-dive)

Input and output electrical specifications

Point: Understand input frequency limits, supported output formats, and voltage/drive constraints before layout. Evidence: See "Input Clock Characteristics" and "Output Electrical Characteristics" tables in the datasheet for thresholds, drive strength, and supported formats. Explanation: The SI53306-B-GMR accepts input clocks up to 725 MHz (max input frequency entry). Outputs can be configured as differential CML/HCSL/LVDS/LVPECL or single‑ended LVCMOS depending on mode strap or register settings; each format has specific VOH/VOL or VOD/VOS limits in the "Output Electrical Characteristics" table. VIH/VIL thresholds for input pins and mode pins are detailed in the "DC Characteristics" table—verify VDDIO-dependent thresholds when selecting LVCMOS levels. Drive capability and recommended load (e.g., 50 Ω single-ended or 100 Ω differential) are specified per output format; those entries inform termination and series resistor choices.

Power, thermal, and package details

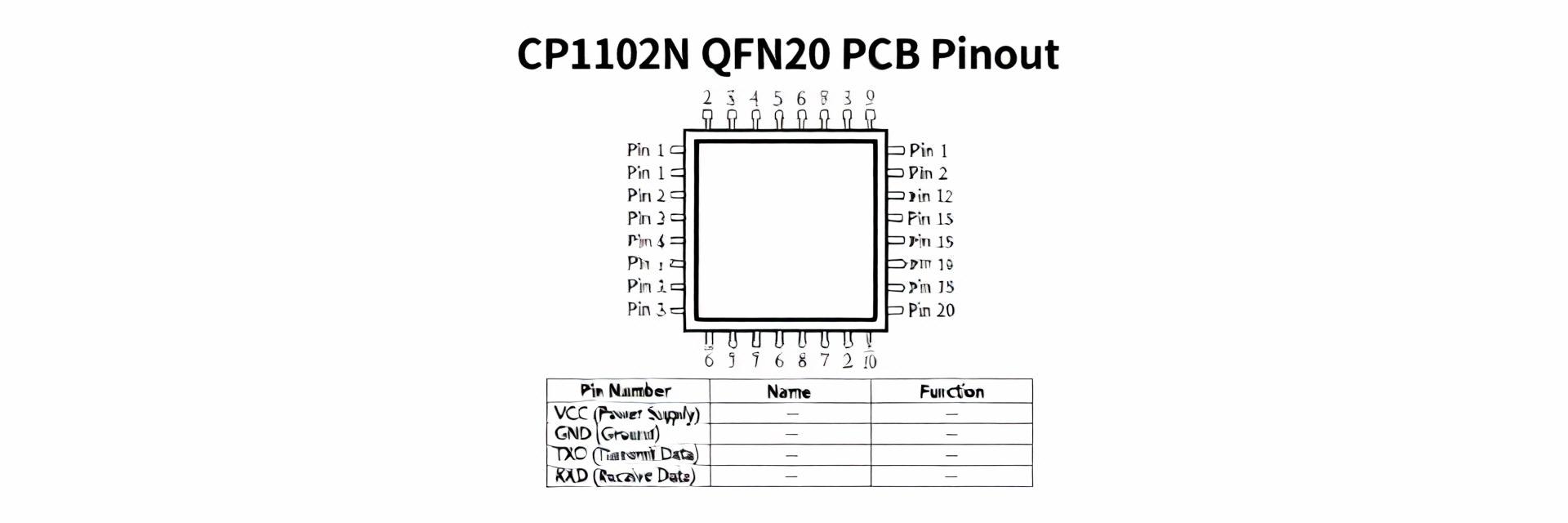

Point: Power rails, current consumption, thermal limits, and package footprint affect BOM and thermal management. Evidence: Consult the "Recommended Operating Conditions", "DC Supply Current" table, and "Thermal Characteristics" / "Package Outline" figures in the datasheet. Explanation: The datasheet lists VDD and VDDIO ranges and typical ICC values under specified conditions; use the "DC Supply Current" table to estimate total board power and decoupling needs. The operating junction and ambient thermal limits, along with θJA/θJC values in "Thermal Characteristics", drive copper pour and via stitching decisions. The SI53306-B-GMR is typically offered in a compact QFN/land-grid package (see the "Mechanical Drawing" figure)—verify the ordering code for the exact package variant and review the solder-paste and pad recommendations in the mechanical section before generating the PCB footprint.

Timing, jitter, and skew specifications

Point: Jitter, phase noise, propagation delay, and skew determine whether the device meets system timing budgets. Evidence: Review the "Phase Noise", "Additive Jitter", and "Timing and Skew" tables and figures in the datasheet. Explanation: The datasheet supplies additive RMS jitter (integrated over specified band, e.g., 12 kHz–20 MHz) and phase-noise plots for typical output formats; additive jitter values should be combined in quadrature with source jitter when calculating overall timing budget. Propagation delay and output-to-output skew entries dictate deskew margin for parallel SERDES lanes—use worst-case skew numbers from the "Timing" table when allocating phase budget. Where phase noise is critical, use the provided phase-noise plots (referenced figure in datasheet) to model oscillator/PLL interactions. For link budget calculations, use datasheet additive jitter + source jitter + channel-induced jitter to predict BER impact at a given data rate.

3 — Pinout & Pin Functions (detailed pinout)

Pin map summary and recommended figure

Point: A clear pin map is essential before layout; label each power, ground, input and output pin explicitly. Evidence: Use the "Pinout Diagram" figure and the "Pin Description" table in the datasheet to capture exact pin numbers. Explanation: Reproduce a pin map that labels VDD, VDDIO, multiple GND pins, input pin(s) (CLK_IN), outputs OUT0–OUT3 with their pin numbers, mode/strap pins (e.g., MODE0/MODE1 or FORMAT pins), OE/RESET, and any NC pins. Include the exact pin numbers from the datasheet's pin diagram and the adjacent "Pin Description" table. For documentation, place a labeled figure (the datasheet's pin diagram) and an adjacent table listing pin number, net name, function, and recommended PCB land pattern references so layout engineers can map nets directly to the footprint.

Pin electrical characteristics & recommended decoupling

Point: Follow per-pin electrical limits and decoupling guidance to avoid functional issues. Evidence: Consult "DC Characteristics", "Absolute Maximum Ratings", and the "Recommended Decoupling" notes/figures in the datasheet. Explanation: Per-pin DC limits (max currents, VDDIO ranges) are found in the DC tables—respect VDDIO maximums for mode pins to avoid latch-up. Decoupling guidance: place a 0.1 µF ceramic capacitor within 1–2 mm of each VDD and VDDIO pin, add a 1 µF (or larger) bulk capacitor on the local supply rail, and consider a 10 µF bulk on the main regulator output; follow the datasheet ESR recommendations where given. Also follow recommended placement for any AC-coupling capacitors on high-speed outputs (the datasheet will specify when AC coupling is required and the recommended capacitor value and voltage rating).

Pin-selectable modes & configuration pins

Point: Pin straps and mode pins determine output format and divider settings for out-of-the-box operation. Evidence: See the "Pin Strapping and Mode Configuration" table and example truth tables in the datasheet. Explanation: The SI53306-B-GMR supports pin-selectable output format and divider via strap pins or programmable registers depending on the specific SKU and firmware. The datasheet provides a truth table showing combinations of MODE/FORMAT pins that produce LVDS, LVCMOS, CML, etc. For example, pulling FORMAT pin high with VDDIO selected to an LVDS-compatible level selects differential outputs; setting MODE pins to particular binary values can set an integer divider or bypass mode. Include the datasheet truth tables or reproduce them in the design notes to ensure correct initial configuration at power-up before any I2C/SPI configuration is applied.

4 — Implementation Guide: PCB Layout, Power, and Signal Integrity

Power-supply filtering and grounding best practices

Point: Proper power filtering and ground strategy reduce jitter and EMI. Evidence: See the "Application Guidelines" and "Layout Recommendations" sections/figures in the datasheet and related application notes. Explanation: Use separate analog/digital planes if recommended; tie grounds with multiple vias and maintain a contiguous ground plane under the SI53306-B-GMR. Place decoupling caps (0.1 µF) within 1–2 mm of each VDD pin and add a 1 µF to 10 µF bulk cap near the regulator output. If the datasheet suggests ferrite beads or LC filters on VDDIO to isolate noisy IO domains, follow those BOM suggestions. Provide a short, low-impedance path from decoupling caps to device pins and avoid routing high-speed signals under the device if it interferes with thermal vias or ground stitching. Follow the datasheet's recommended BOM list for best results in minimizing supply-induced phase noise.

Routing outputs by format: CML/HCSL/LVDS/LVCMOS practical tips

Point: Each output format has distinct routing and termination rules that affect signal integrity. Evidence: The "Application Circuits" and "Output Termination" examples in the datasheet list recommended circuits per format. Explanation: For differential outputs (CML, LVDS, LVPECL), route as controlled-impedance differential pairs (typically 100 Ω differential) with matched lengths and symmetry; place differential termination (100 Ω) close to the receiver or at the driver per the datasheet recommendation. For CML/HCSL, AC coupling and series resistors may be required—follow the example schematics for proper DC biasing and series resistance. LVCMOS outputs require single-ended routing with proper series resistor (e.g., 22–33 Ω) to damp reflections when driving 50 Ω traces. Provide test points or velocity-matched probe points as recommended by the datasheet to enable accurate measurement without loading the line excessively.

Thermal, footprint, and assembly notes

Point: Correct footprint and thermal measures prevent solder defects and ensure reliability. Evidence: Refer to the "Package Mechanical Dimensions" and "Reflow and Assembly" notes in the datasheet. Explanation: Use the datasheet's recommended solder-pad dimensions and stencil recommendations exactly to avoid tombstoning or voiding. For thermal management, include an exposed pad (if present) tied to ground with multiple thermal vias to inner planes; the "Thermal Pad Recommendations" figure shows suggested via diameter, count and spacing. Follow the reflow profile limits in the datasheet to comply with peak temperature and time-above-liquidus parameters. Where high ambient dissipation is expected, increase copper pour and add stitching to reduce θJA and maintain device junction temperature within the datasheet-specified limits.

5 — Testing, Troubleshooting & Example Use Cases

Common integration issues & datasheet cross-checks

Point: Quickly cross-check datasheet tables when common faults appear at bring-up. Evidence: Use "Power-Up Sequencing", "Pin Strapping", "DC Characteristics", and "Absolute Maximum Ratings" tables for diagnostics. Explanation: Typical problems include no output (check VDD and VDDIO presence and levels, verify OE/RESET strap state, and confirm input clock presence and amplitude against "Input Clock Characteristics"), incorrect format (verify mode strap truth table and VDDIO level for LVCMOS thresholds), and high jitter (check supply decoupling and supply noise per "Phase Noise" notes). Create a quick diagnostic checklist: 1) Verify all recommended supply voltages and decoupling, 2) Check strap pins for correct pull-ups/pull-downs and mode selection, 3) Confirm input clock amplitude and frequency under "Input Clock Characteristics", 4) Measure outputs with proper termination and load as per "Output Electrical Characteristics".

Test procedures & measurement tips

Point: Accurate measurement of jitter, skew, and delay requires controlled fixtures and instrument settings. Evidence: See the "Measurement and Test" recommendations in the application notes section of the datasheet. Explanation: For jitter, use a phase-noise analyzer or high-bandwidth sampling scope with low-jitter reference; integrate phase-noise or jitter over the same frequency band listed in the datasheet (e.g., 12 kHz–20 MHz) for direct comparison. For propagation delay and skew, use differential probes with matched impedance and minimize probe stub lengths; trigger on the input and measure differential outputs with the same probing configuration. Use AC coupling where the datasheet specifies it and implement the recommended terminations to avoid measurement artifacts. Recommended instruments include 6+ GHz scopes with low-noise probes and a spectrum/phase-noise analyzer for accurate phase-noise plots.

Example reference designs and alternative parts

Point: Two concise use cases illustrate integration choices and potential alternative parts. Evidence: Datasheet "Application Diagrams" plus "Device Selection" guidance. Explanation: Example 1 — FPGA clock fanout: feed a clean XO or Si533xx PLL output into SI53306-B-GMR CLK_IN, strap outputs to LVCMOS for FPGA bank A and LVDS for SerDes transceivers; use per-output resistive terminations per the "Application Circuits" figure. Example 2 — multi-protocol link head: use SI53306-B-GMR to generate matched CML outputs for multiple PHY lanes, ensuring AC coupling and receiver biasing as shown in datasheet termination diagrams. Alternatives: For higher fanout or integrated PLL functions, evaluate other Si5330x family members or competing devices from other vendors with integrated Jitter Attenuators or different package options—consult the datasheet's "Related Parts" table for comparable SKUs and footprints.

Summary

- The SI53306-B-GMR is a flexible 1:4 fanout clock buffer supporting up to 725 MHz input and multiple output formats; consult the datasheet for format and supply tables to match your system needs.

- Key implementation items: follow the datasheet pinout and pin-description table, apply close decoupling (0.1 µF per VDD pin + bulk caps), and use format-specific terminations shown in the application circuits.

- For testing and bring-up, use the datasheet timing, jitter, and thermal tables to build a measurement checklist and to size power and thermal mitigation correctly for reliable operation.

FAQ

What are the essential datasheet items to verify before layout for SI53306-B-GMR?

Verify recommended operating voltages and absolute maximum ratings, pin descriptions and exact pin numbers from the pinout table, and the "Output Electrical Characteristics" for termination and drive details. Confirm thermal pad and footprint dimensions from the mechanical drawing and consult the "DC Supply Current" table to size regulators and decoupling. Cross-check strap/mode truth tables to guarantee correct default output formats at power-up.

How should I terminate SI53306-B-GMR outputs for CML and LVDS?

For differential LVDS, use a 100 Ω differential termination across the pair close to the receiver. For CML/HCSL-style outputs, follow the application circuits: often AC-couple then bias or use series resistors (e.g., 22–50 Ω) and recommended pull networks as shown in the datasheet examples. Always place terminations close to the receiver and adhere to the output format-specific guidance in the "Output Termination" figures.

What are quick checks if outputs are missing or in the wrong format?

Check VDD and VDDIO rails for correct voltages and decoupling, verify mode/strap pins are set to the intended states and that OE/RESET is not asserted, confirm the input clock amplitude and frequency against the "Input Clock Characteristics" table, and ensure output loads and terminations match the "Output Electrical Characteristics". Use the datasheet’s diagnostic checklist (power rails, strap pins, input frequency limits) to quickly isolate the issue.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- SI3402-B-GMR PoE PD Controller: Market & Specs Report

- SI3402-B-GMR Benchmarks: Real PoE Performance Insights

- EFM8BB21F16G Full Datasheet & Pinout: Specs Summary

- CP2102N-A02-GQFN20R Pinout & Footprint: Quick Data Guide

- SI53307-B-GMR Datasheet & CAD Models: Quick Specs Checklist

- SI53361-B-GMR: Latest Specs, Stock Levels & Price Guide

- SI53340-B-GM: Deep Performance Report & Key Metrics

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606