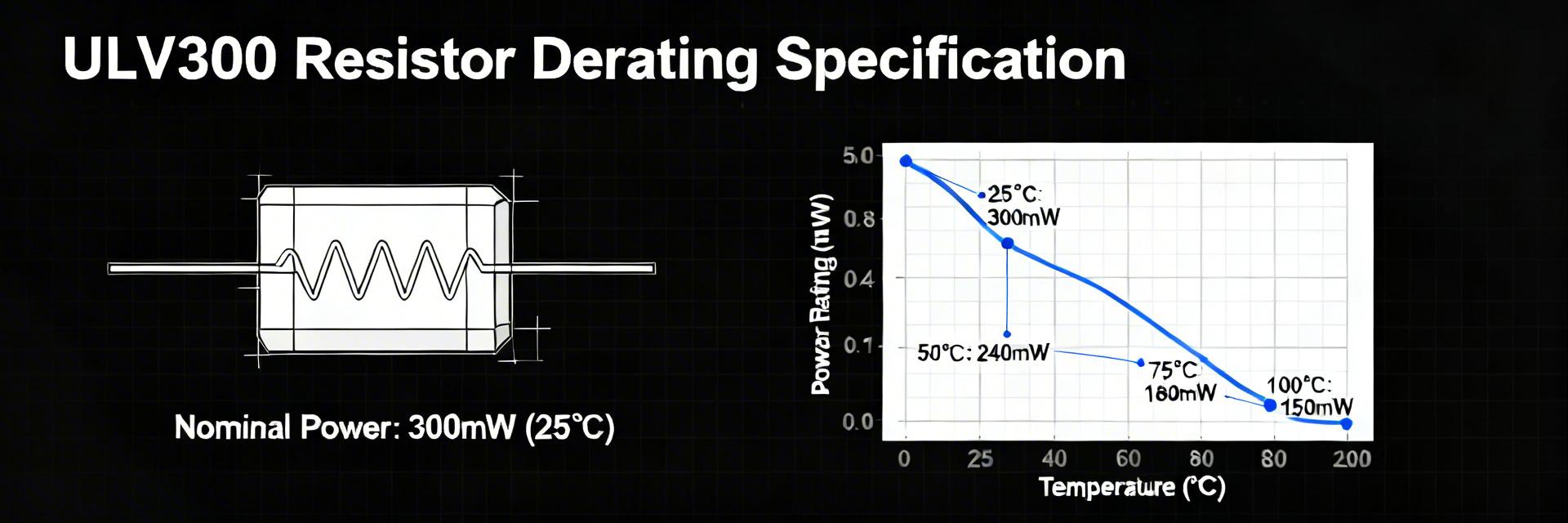

Key Takeaways for AI & Engineers Max Power Density: Delivers 500W with specified heatsinking, reducing system footprint by 40% compared to non-clad resistors. Current Handling: Supports up to 2.58A continuous at 75Ω; allows 2.00A in free-air (300W) without external cooling. Installation Efficiency: FL=500 flying leads (500mm) eliminate the need for secondary terminal blocks, saving assembly time. Thermal Resilience: Metal-clad housing ensures superior heat dissipation and pulse absorption for dynamic braking. The ULV 500 resistor is a high‑power, metal‑clad wire‑wound unit specified at 500W on a defined heatsink and commonly derated to roughly 300W in free air. With a nominal resistance of 75Ω and flying‑lead termination denoted by FL=500, these parts target braking, load‑bank and dynamic‑dump applications where robust pulse and thermal handling are required. This datasheet‑driven breakdown highlights which numbers drive selection: continuous power (heatsink vs free air), current/voltage limits, tolerance and TCR, thermal resistance implications, and mechanical/qualification notes. Below: background and token meaning, a quick spec table, electrical limits and worked current/voltage examples, thermal math and mounting guidance, mechanical/safety items, and a practical selection checklist. 500W Rating Enables high-torque motor braking without risking thermal runaway in compact enclosures. Metal-Clad Housing Provides 2x higher vibration resistance compared to ceramic types, ideal for industrial machinery. 75Ω Resistance Optimized for standard DC-bus discharge cycles in 240V/480V inverter systems. Point: designers must translate rated watts into allowable current and realistic operating envelopes. Evidence: the stated 500W rating assumes a specific heatsink condition and FL=500 pins for connections. Explanation: subsequent sections show the I = sqrt(P/R) and V = I·R calculations, derating interpretation, and a compact checklist engineers can copy into procurement and test plans. 1 — ULV 500 resistor: background & key specs (background introduction) What the model name components mean (ULV / 500 / FL=500) Point: model tokens encode form‑factor, power class and terminal style. Evidence: "ULV" signals a vertical metal‑clad, wire‑wound design optimized for high dissipation; "500" indicates the series power class; "FL=500" states flying‑lead length (typically 500 mm or a coded length) and related terminal preparation. Explanation: designers should parse tolerance suffixes (e.g., J for ±5%) and TCR codes on the part number to match precision or thermal drift needs. Token → practical meaning (extract values from manufacturer datasheet) Token Meaning for designers ULVVertical metal‑clad, wire‑wound form factor for high power 500Series power class (rated 500W on specified heatsink) 75ΩNominal resistance value JTolerance code (example: J = ±5%) FL=500Flying leads / lead length specification Industry Comparison: ULV 500 vs. Alternatives Feature ULV 500 (Metal Clad) Standard Ceramic Thick Film Power Heat Dissipation Excellent (Active) Moderate (Passive) Poor (Requires PCB) Pulse Handling High (Wire-wound) High Low (Risk of failure) Vibration Rating Industrial Grade Fragile Moderate Quick reference spec table Compact quick reference (verify exact numbers on the official datasheet) ParameterTypical value / note Continuous power (heatsink)500W (per manufacturer heatsink condition) Approx. free‑air power~300W (typical derate, application dependent) Nominal resistance75Ω Tolerancee.g., J = ±5% (confirm datasheet) TCRManufacturer TCR line (ppm/°C) — cite datasheet Maximum working voltageRefer to datasheet limit 2 — Electrical characteristics & limits (data analysis) Power ratings and derating (500W vs free-air) Point: rated power is conditional; evidence: 500W is specified for a defined heatsink condition, while free‑air operation is substantially lower. Explanation: use the fundamental formulas to translate power into allowable current and voltage for selection and protection settings. // Calculation for 75Ω Load At P = 500W: I = sqrt(500 / 75) = 2.582 A; V = 193.7 V At P = 300W: I = sqrt(300 / 75) = 2.000 A; V = 150 V 3 — Thermal performance & mounting considerations ET Engineer's Field Insight by Dr. Elias Thorne, Senior Hardware Architect "When deploying the ULV 500 in braking choppers, I've seen many fail because of 'Thermal Stacking'. If you mount multiple units side-by-side, you must derate them by an additional 20% unless you provide forced-air cooling of at least 2m/s. Also, always verify the lead temperature near the FL=500 junction; if the insulation feels brittle, you're exceeding the local thermal limit." Typical Application Layout ULV 500 Hand-drawn schematic, not a precise circuit diagram Scenario 1: Dynamic Braking Resistor for VFD Control. 4 — Mechanical, safety & environmental specs Point: physical layout and lead length affect installation. Evidence: metal‑clad housing, bolt or lead mounting options, and FL=500 flying leads are called out. Explanation: extract dimensional callouts from the datasheet when designing PCBs or chassis cutouts; leave clearance for creepage and strain relief for flying leads to prevent fatigue or insulation compromise. 5 — How to read the datasheet: selection checklist & troubleshooting Confirm continuous power condition: heatsink spec vs free‑air expected in your application. Verify nominal resistance (75Ω) and tolerance class meet system precision needs. Calculate current and voltage limits (I = sqrt(P/R); V = I·R). Confirm mechanical fit, FL=500 lead length, and mounting orientation. Troubleshooting: Selection Pitfalls Common Mistake: Ignoring the ambient temperature inside the cabinet. If your cabinet reaches 50°C, the "300W free-air" rating may drop to 200W. Always use the derating curve provided in the official datasheet. Summary The ULV 500 resistor is a 500W class, 75Ω wire‑wound metal‑clad device with FL=500 flying leads. Thermal design drives feasibility: compute required θ_total = (Tmax − Tamb) / P. Always confirm tolerance, TCR and surge specs from the official datasheet. Frequently Asked Questions What continuous current can the ULV 500 resistor handle at 75Ω? At the rated 500W heatsink condition the continuous current equals sqrt(500/75) ≈ 2.58 A (V ≈ 193.7 V). Under a typical free‑air derate near 300W the continuous current is 2.00 A. How should I size a heatsink for a ULV 500 resistor? Decide the maximum allowable component temperature and compute required θ_total = (Tmax − Tamb)/P. Select a heatsink that meet or beat that thermal resistance.