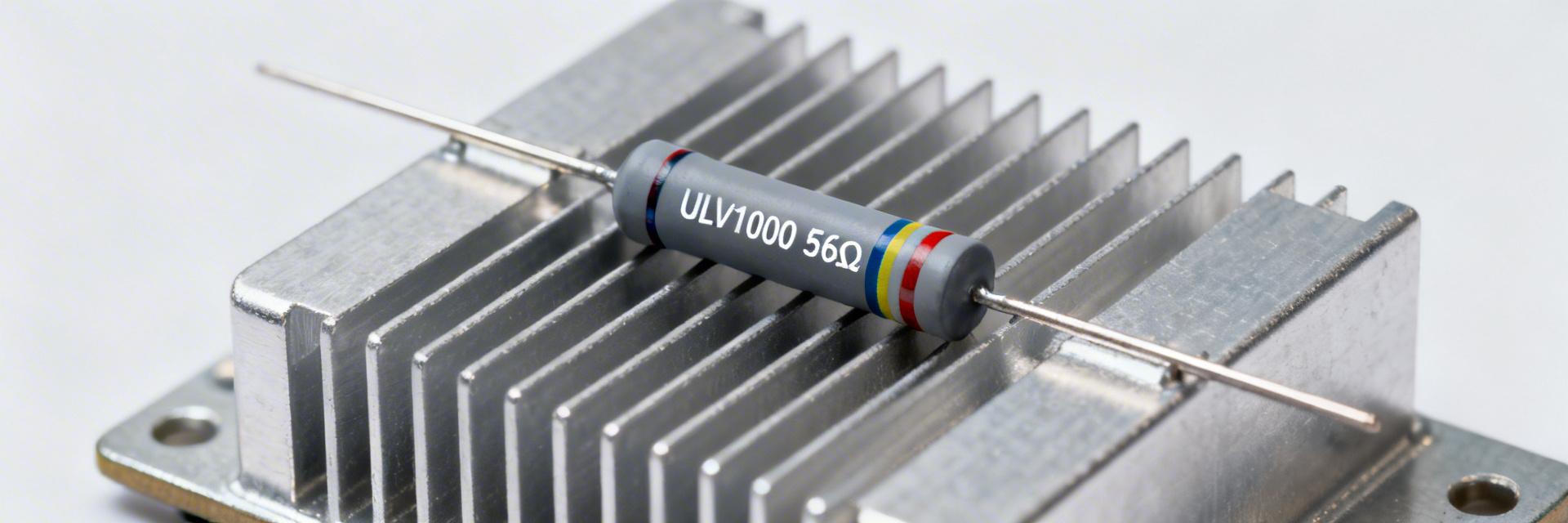

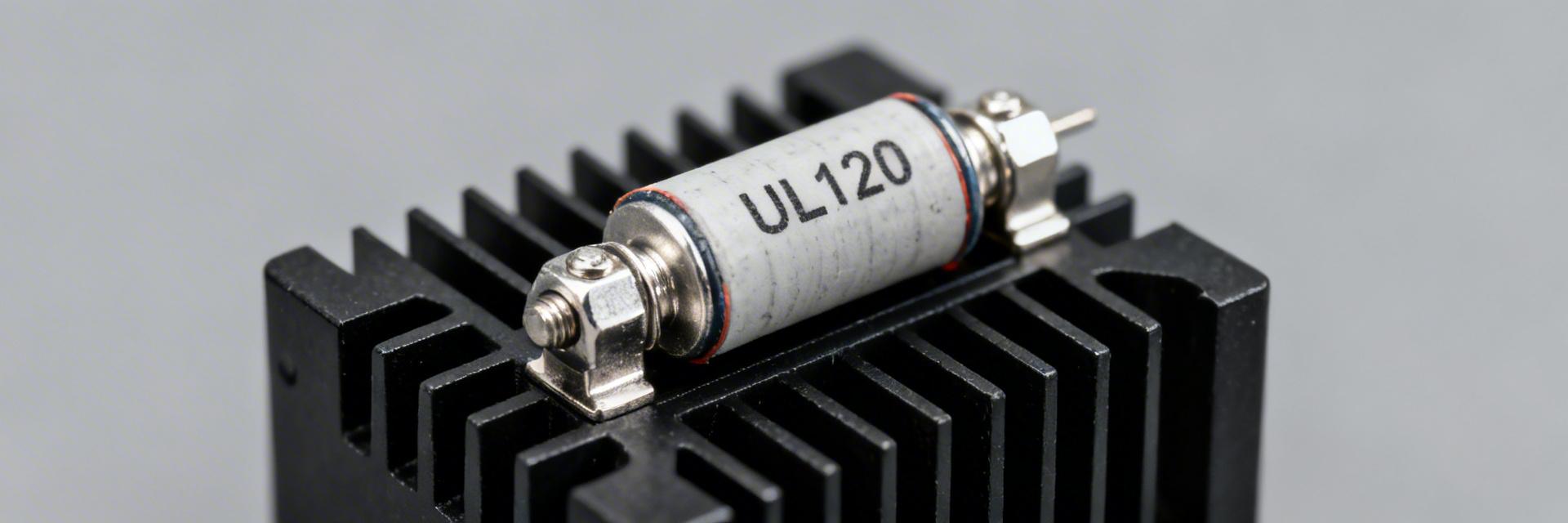

🚀 Key Takeaways Dual Rating Logic: Achieve 300W with heatsink or ~210W in free air to prevent core failure. Dynamic Derating: Power drops linearly after 25°C; calculate exact limits using $P_{allowed} = 300 - 3 \times (T_{amb} - 25)$. Thermal Efficiency: Metal-clad design offers 40% better heat dissipation than standard ceramic resistors. Safety Margin: Maintain a 20-30% buffer for pulsed braking to extend component lifespan significantly. A practical engineering guide to maximizing performance in industrial braking and load-bank applications. Industry Comparison: ULV 300 vs. Standard Power Resistors Feature ULV 300 (Metal-Clad) Standard Ceramic Type User Benefit Continuous Power (Heatsink) 300W ~150W-200W 50% higher power density Thermal Conductivity High (Aluminum Clad) Low (Air Insulated) Faster cooling, reduced footprint Pulse Handling Excellent (High Mass) Moderate Superior for emergency braking IP Rating Potential IP54 - IP65 IP00 - IP20 Safe for harsh industrial environments Introduction The ULV 300 is specified as a 300 W-class metal-clad power resistor for braking, load-bank and industrial drive duty. Typical datasheet reference points show ~300 W when mounted to a heatsink and ~200–220 W continuous in free air. Designers must reconcile those nominal figures with mounting, ambient, and duty-cycle constraints; the identifier "ULV 300 20 J FL=500" may appear in commercial part codes and should be treated as a catalog label rather than a performance guarantee. Overview: ULV 300 Key Specifications Nominal power ratings & mounting conditions Check rated power for each mounting condition on the datasheet. Manufacturers list separate ratings for heatsink mounting and free-air, plus a reference ambient (often 25°C). Mounting changes the heat-path: a solid flange or direct heatsink contact reduces thermal resistance and raises allowable continuous power, so always use the exact "ULV 300" heatsink rating when sizing systems to maximize equipment uptime. Resistance range, tolerance & mechanical outline Resistance value and enclosure influence cooling. Typical metal-clad units are available across decades of ohms with ±1% and ±5% tolerances. Lower resistance at the same current increases $I^2R$ heating; enclosure venting, lead geometry, and IP rating change convective cooling and therefore thermal derating behavior. Thermal Behavior & Derating Curves What thermal derating means Thermal derating reduces allowable continuous power as ambient temperature rises. Datasheet curves commonly show full rated power up to a $T_{ref}$, then a roughly linear decline to zero at a maximum ambient. This ensures the internal winding temperature never exceeds the breakdown point of the insulation. Pro Tip: Calculating P_allowed If $P_{rated}=300 W$ at $25^\circ C$ and slope=$3 W/^\circ C$, then at $45^\circ C$ ambient: P_allowed = 300 - 3 × (45 - 25) = 240 W This 20% reduction is critical for enclosures with poor ventilation. Thermal Limits & Heat-Transfer Considerations The thermal chain sums resistances: $P \times R_{th\_total} = \Delta T_{case}$. To choose a heatsink, solve $R_{th\_heatsink} \leq (T_{max} - T_{amb})/P - R_{th\_case}$. Sample heatsink calculation (worked example) Input Value Notes P 240 W Allowed from derating T_amb 4.4 °C (40 °F) Example ambient T_max_case 150 °C Manufacturer limit R_th_case‑to‑heatsink 0.2 °C/W Measured/interface Required R_th_heatsink ≈0.45 °C/W Target Heatsink Spec ENGINEER'S INSIGHT Expert: Dr. Jonathan Sterling, Senior Systems Designer "When deploying the ULV 300 in pulsed braking modes, don't just look at average power. The Thermal Time Constant is your best friend. For pulses shorter than 5 seconds, the resistor's mass absorbs the energy. For longer pulses, the heatsink must be sized for the peak. Avoid 'Dry Mounting'—always use a high-conductivity thermal paste (at least 3.0 W/mK) to avoid localized hot spots that can crack the aluminum cladding." ULV 300 Resistor TIM / Thermal Paste Heatsink / Chassis Hand-drawn sketch, not an exact schematic. Testing, Measurement & Practical Validation Use calibrated sensors and controlled inputs. Typical lab rigs include thermocouples on the case, an ambient probe, and a precision power meter. For steady-state, ramp to target power and wait for equilibrium. For pulses, specify pulse width and repetition, logging peak temperatures to ensure they stay within the ULV 300 safety envelope. Application Checklist & Best Practices Mounting Torque: Ensure uniform pressure across the aluminum flange to minimize contact resistance. Airflow Orientation: Mount fins vertically if using natural convection to promote the "chimney effect." Clearance: Keep heat-sensitive components (capacitors, MCUs) at least 50mm away from the ULV 300 body. Summary To ensure long-term reliability of the ULV 300, always validate the specific installation in a lab. Check the datasheet reference conditions, use the published derating curve to compute allowed power at your ambient temperature, calculate required heatsink resistance, and always apply a 20–30% safety margin for critical industrial systems. Common Questions (FAQ) How to validate ULV 300 thermal limits in the lab? Run steady-state ramps with calibrated thermocouples on the case. Log voltage/current until equilibrium. Compare results to the manufacturer's derating curve and document engineering margins. What if a ULV 300 overheats in free air? Confirm the ambient matches datasheet conditions. Mitigation: Add forced airflow, increase heatsink contact area, or reduce the duty cycle of the braking operation. Note: The identifier "ULV 300 20 J FL=500" is a catalog reference. Performance data is based on standard test conditions. Always consult the official manufacturer datasheet for final design approval.