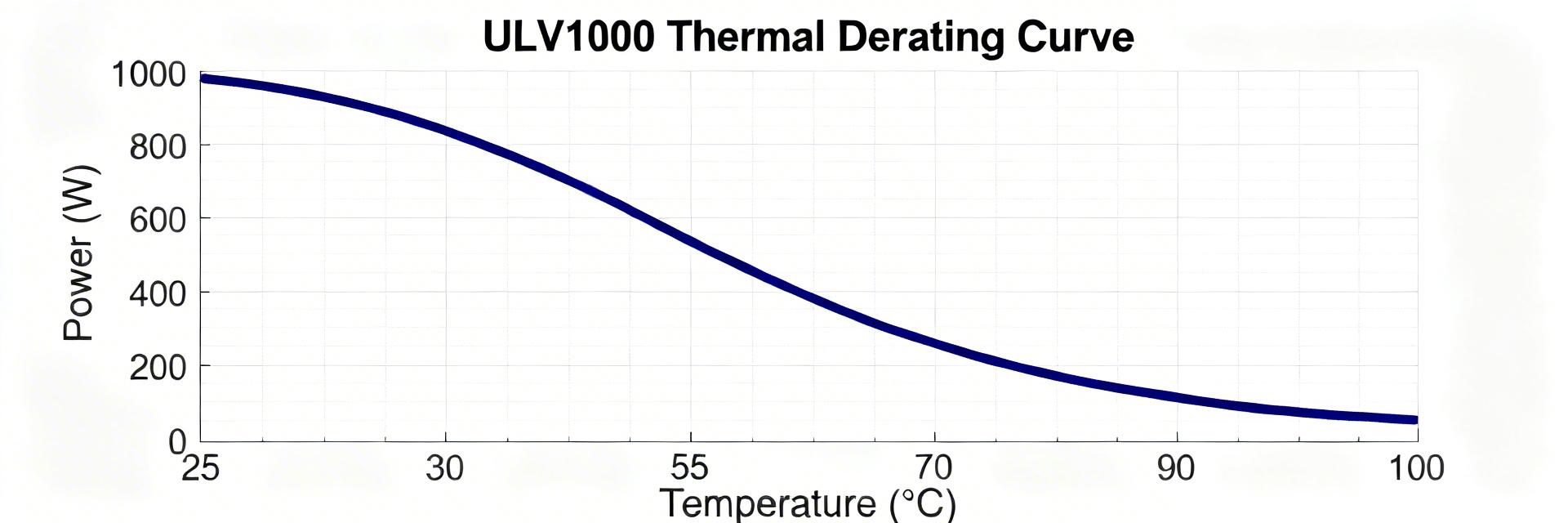

Key Takeaways 500W Performance: Full power requires specific heatsink mounting. Thermal Derating: Power drops to ~300W in free air. Industrial Use: Ideal for motor braking and load testing. Safe Design: Metal-clad housing ensures high dielectric strength. Point: The ULV 500 resistor is a high-power, industrial braking and load resistor specified for up to 500 W when mounted on a defined heatsink and commonly derated to roughly 300 W in free air. Evidence: Typical thermal notes indicate power capability falls sharply above moderate ambient temperatures. Explanation: This article explains how to read a ULV 500 resistor datasheet, interpret thermal behavior, and choose installation and heatsinking to ensure reliable operation under expected loads. Point: Readers will gain practical calculation methods and installation checklists. Evidence: The write-up covers electrical limits, mechanical callouts, and thermal modelling. Explanation: Engineers, purchasers, and technicians will be able to extract the critical fields from a datasheet, run quick P=I²R or P=V²/R checks, and validate mounting and thermal margins before purchase or commissioning. Competitive Comparison: ULV 500 vs. Standard Ceramic Resistors Feature ULV 500 (Metal Clad) Standard Wire-wound User Benefit Power Density High (500W w/ Heatsink) Medium Saves ~20% PCB/Panel space Vibration Resistance Excellent (Encapsulated) Moderate Reliable in mobile/industrial apps Thermal Response Rapid via Chassis mount Slow (Air convection) Prevents localized hotspots 1 — Overview & key specifications (background) 1.1 — What the model name denotes and typical use cases Point: The ULV 500 resistor family denotes a high-dissipation, metal-clad or wire-wound unit designed for braking, dynamic load, and resistive dump applications. Evidence: These parts are specified for continuous high-power dissipation on heatsinks and are often mounted vertically or horizontally to match airflow. Explanation: Typical uses include motor braking banks, transient load testing racks, and resistive discharge circuits in industrial environments where space, forced air, and bolt-down mounting are available; the ULV 500 resistor is chosen where predictable thermal management is required. 1.2 — At-a-glance spec list to include from the datasheet Point: A concise spec table speeds procurement and comparison. Evidence: Extract rated power, resistance range, tolerances, temperature coefficient, and mechanical details directly from the datasheet. Explanation: Use the checklist below for quick qualification and to flag missing items to suppliers. Parameter Typical Entry Rated power 500 W (on specified heatsink), derated in free air Resistance range & steps Manufacturer-specified Ω range and step increments Tolerance % options (e.g., ±1%, ±5%) Temperature coefficient ppm/°C Maximum working voltage Specified VDC/AC Insulation / dielectric Withstand voltage and creepage distances Case dimensions & weight Drawing callout with tolerances Terminal type & mounting Studs, lugs, torque, and hole pattern 🛡️ Engineer’s Insight: High-Power Layout "When deploying the ULV 500, the thermal interface material (TIM) is often the bottleneck, not the heatsink itself. A common mistake is using too much thermal grease, which actually increases resistance. Aim for a thickness of 0.05mm to 0.1mm for optimal flux." — Dr. Marcus Vane, Senior Power Systems Engineer Typical Application: Motor Braking VFD ULV 500 Resistor Hand-drawn sketch, non-precise schematic Quick Troubleshooting Discoloration: Signal of sustained 120%+ overload. Ohmic Drift: Check for micro-cracks in ceramic core. Terminal Arcing: Verify torque meets 2.0 Nm spec. 2 — Datasheet deep-dive: how to read critical fields 2.1 — Electrical specifications and limits Point: Electrical fields define usable limits and safety margins. Evidence: Datasheet lines for resistance value, tolerance, continuous power, pulse ratings, and maximum voltage are the primary constraints. Explanation: Use P = I² × R or P = V² / R to verify currents and voltages: for example, for a 75 Ω resistor at 500 W, Imax = sqrt(500/75) ≈ 2.58 A and Vmax = Imax × R ≈ 193 V; check pulse ratings separately and derate continuous values per the datasheet. 2.2 — Mechanical and environmental specs to verify Point: Mechanical callouts prevent installation failures. Evidence: Drawings show mounting-hole pattern, terminal clearances, recommended torque, and creepage/clearance. Explanation: Verify ambient operating range, IP or ingress notes, and shock/vibration ratings; if mounting tolerances or torques are absent, request detailed drawings—missing mechanical data is a common procurement gap that can lead to poor thermal contact or electrical shorts. 3 — Thermal behavior & derating (data + method) 3.1 — Interpreting thermal charts and derating curves Point: Derating curves map ambient temperature to allowable power. Evidence: Datasheet thermal charts often use a reference temperature (e.g., 25°C) and show linear or piecewise derates to a maximum ambient. Explanation: Read the curve by locating ambient on the x‑axis and drawing down to the curve to read allowable power; as an example method, with a reference of 25°C at 500 W and a linear derate to 0 W at 125°C, allowable power at 50°C = 500 × (1 − (50−25)/(125−25)) = 375 W—apply the specific datasheet curve for precise values. 3.2 — Heat-transfer calculations and practical thermal modelling Point: Combine thermal resistances to estimate temperature rise. Evidence: Use Rth_resistor–heatsink and Rth_heatsink–ambient to get Rth_total; temperature rise = P × Rth_total. Explanation: For steady-state check, sum Rth values (K/W). Example: if Rth_total = 0.2 K/W and P = 375 W, ΔT = 75 K. Add ΔT to ambient to estimate component temperature. For pulsed loads include thermal time constant and use conservative margins; verify assumptions in-situ with IR or thermocouples. 4 — Mounting, heatsinking & installation best practices 4.1 — Heatsink selection and mounting method Point: Heatsink choice is the primary lever to meet thermal limits. Evidence: Select a heatsink with thermal resistance low enough that Rth_total keeps junction and case below maximum at expected power. Explanation: Ensure mating surfaces are flat, use thin, electrically compatible TIM where required, and follow a controlled torque sequence to avoid uneven contact; consider forced airflow and mounting orientation described in the datasheet when sizing the heatsink. 4.2 — Wiring, fusing, and safety considerations Point: Proper wiring and protection prevent thermal and electrical failures. Evidence: Terminal ratings and maximum continuous current guide conductor sizing; fusing protects against sustained overloads. Explanation: Use conductors sized for continuous current with temperature rating above expected operating temperature, place a fuse or circuit breaker sized to allow expected inrush but protect sustained overload, and verify electrical isolation if required. Checklist: inspect terminal torque, verify clearances, and confirm protective devices before energizing. 5 — Selection checklist, testing & troubleshooting 5.1 — Pre-purchase and specification checklist Point: A short pre-purchase checklist reduces mismatches. Evidence: Confirm rated power and derating curves, resistance availability and tolerances, mounting dimensions, terminal type, ambient rating, and procurement lead times. Explanation: Require the datasheet PDF and engineering drawing; if derating curves or mechanical tolerances are missing, request supplier clarification before ordering to avoid returns or field failures. 5.2 — In-field testing and common failure modes Point: Field verification validates installation and thermal performance. Evidence: Procedures include resistance verification at ambient, controlled IR profiling under a known load, and thermal imaging to find hotspots. Explanation: Common symptoms of poor contact or overload include drift in resistance, discoloration, hotspots on the case, or eventual open circuit. Recommended equipment: precision ohmmeter, controlled DC load, thermocouples/IR camera. Pass/fail: stable resistance within tolerance and absence of hotspots at rated derated power. Summary Point: The ULV 500 resistor delivers high-power dissipation when paired with proper heatsinking and installation. Evidence: Reading the datasheet for continuous power, derating curves, mechanical tolerances, and terminal ratings is essential to predict in-service performance. Explanation: Use the datasheet to extract electrical and mechanical limits, run P=I²R or P=V²/R checks, size heatsinks using combined Rth, and validate installations with IR or thermocouples to ensure reliable operation under the intended ambient and load. Technical Reference Article for Industrial Component Selection • Data-driven Insights • 2024 Engineering Guide