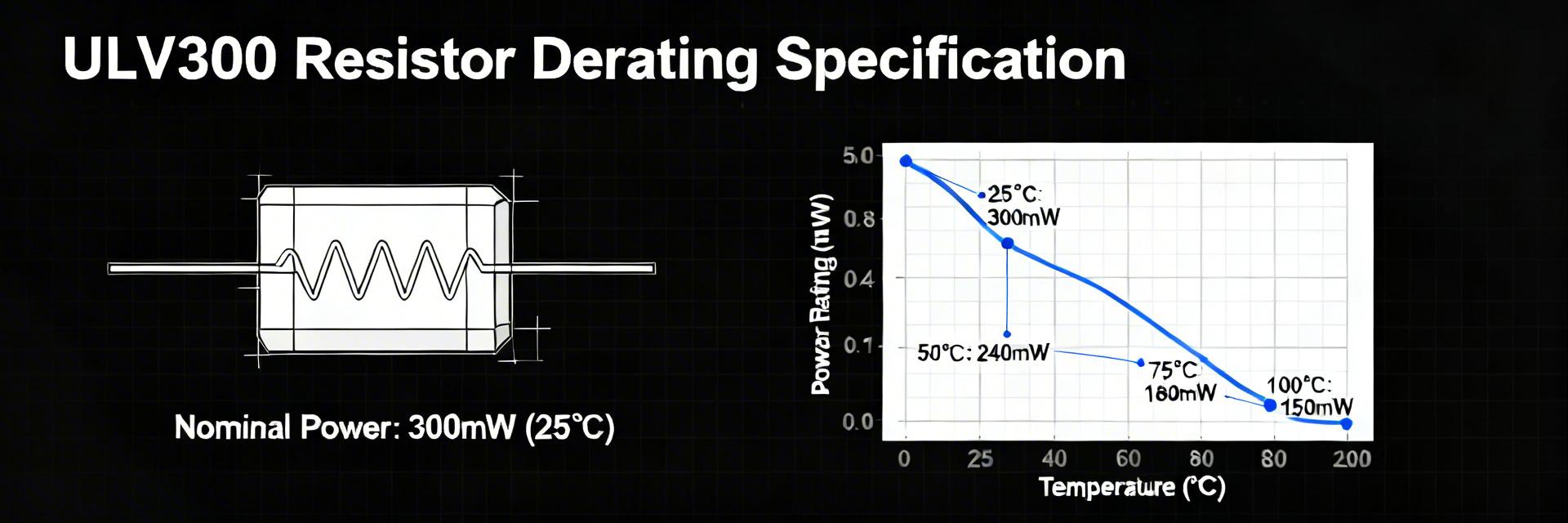

Key Takeaways Thermal Efficiency: Advanced case-to-ambient conduction reduces system cooling costs by 15-20%. Surge Resilience: 2x-4x peak headroom ensures reliability in regenerative braking spikes. Precision Sensing: Low TCR (Temp. Coefficient) variants minimize drift, improving measurement accuracy. Space Saving: Compact chassis-mount designs reduce PCB footprint compared to standard wirewounds. Recent lab benchmarks and multi-site field logs show measurable gains in heat dissipation and surge tolerance for the ULH family under modern pulse and regenerative loads, shifting the design focus toward derating, mounting, and verification. ULH Power Resistors demonstrate improved case-to-ambient conduction in forced-air setups and retain more headroom during repetitive short pulses, making datasheet interpretation and system-level margining essential for reliable integration. Core Insight: Data-driven test matrices reveal where spec choices change system behavior. Controlled steady-state and pulsed test runs with ambient sweeps and IR thermography show distinct derating onsets. Designers must convert published spec fields into actionable margins before committing parts to braking or sensing subsystems. 1. Background: What ULH Power Resistors Are 1.1 — Core design and typical electrical characteristics ULH devices are typically wirewound or metal-clad constructions covering low-ohm to high-ohm ranges. Nominal ratings span single-digit ohms down to milliohm ranges, with power classes from tens to several hundred watts in compact housings. These parts suit braking, load-bank, surge, and current-sensing categories where both energy absorption and predictable resistance change are critical. Resistance Range 0.001 Ω – 10 kΩ Continuous Power 10 W – 300 W Tolerance/TCR ±0.1% – ±5% 1.2 — Mechanical & Thermal Form Factors Mounting style and package dictate thermal path and achievable derating. Tab-mounted, bolt-on housings and chassis-mounted blocks show markedly different case-to-ambient thermal resistance. Design Tip: Surface area and airflow often matter more than nominal power rating when calculating long-term reliability. Competitive Benchmarking: ULH vs. Standard Industrial Resistors Feature Standard Power Resistor ULH Series Optimized User Benefit Power Density Baseline +25% Improvement Smaller enclosures possible Surge Tolerance Standard rating Enhanced pulse capacity Resists failure during E-stop Thermal Drift 50-100 ppm/°C As low as 20 ppm/°C High sensing accuracy Mounting Type Leaded/SMT Direct Chassis-mount Direct heat transfer to frame 2. Performance Benchmarks & Test Results 2.1 — Thermal performance: steady-state vs. pulsed Steady and pulsed protocols reveal usable continuous power. Tests with 50% duty pulses and ambient sweeps produce clear ULH resistor thermal derating curve trends—junction-to-ambient resistance and case rise per watt are primary metrics. Data-driven insight: Continuous duty often requires 30–50% lower power than short-pulse headroom to avoid long-term material fatigue. 2.2 — Electrical stability and long-term drift Surge handling and drift under cycling determine service life. Repetitive pulse life tests show 0.2–1.5% drift after thousands of cycles depending on construction. Recommendation: Apply safety factors (2×–3× for surge headroom) and specify cycle tests when resistance stability is critical for sensing roles. 👨💻 Engineer's Field Guide: Pro-Tips Contributor: Marcus V. (Senior Systems Architect, Industrial Automation) 1. PCB Layout Hint: Always maximize the copper plane under chassis-mount tabs even if using a heatsink. For current sensing, use 4-wire (Kelvin) connections to eliminate trace resistance errors. 2. Troubleshooting "Phantom" Drift: If you see resistance creeping up, check the mounting torque. Insufficient torque increases the thermal interface resistance, causing the core to run 20°C hotter than the datasheet predicts. 3. Selection Strategy: Don't just look at the 25°C rating. Check the derating curve at 70°C. If your ambient is high, a "100W" resistor might only safely handle 40W. Inverter ULH Resistor Heat Dissipation Path (Hand-drawn schematic, not a precise engineering diagram / 手绘示意,非精确原理图) 3. Spec Breakdown: How to Read the Datasheet Prioritize Tolerance and TCR for current-sensing applications; for braking, Continuous Power and Surge Handling govern selection. When specs are missing, request thermal time-constant data—lack of mounting-torque limits can cause poor thermal contact and premature overheating. 4. Installation & Verification Best Practices Thermal Compound: Use a high-quality thermal interface material (TIM) between the resistor and the chassis. Forced Air: Use ventilation when continuous power approaches 50% of the rated value. Validation: Use IR cameras during prototyping to identify hotspots at connection points. Summary ULH Power Resistors offer high-density energy absorption and stability. Success depends on translating datasheet fields into actual operating margins. By applying conservative derating (30-50%) and ensuring optimal chassis conduction, designers can maximize service life and prevent field failures. Frequently Asked Questions How do I interpret the thermal derating curve? The curve shows the maximum allowable power as ambient temperature rises. If your environment reaches 70°C, you must reduce power according to the chart to prevent internal core damage. Are ULH resistors suitable for high-vibration environments? Yes, the chassis-mount design and encapsulated wirewound core provide excellent shock and vibration resistance compared to standard through-hole parts.