Point: Laboratory benchmarking across representative PoE PD builds shows measurable variation in delivered power and system efficiency; engineers evaluating PoE Performance at 15 W loads should expect single-digit to low-double-digit percent spreads between controllers.

Evidence: Controlled tests with steady-state 15 W PD profiles reveal up to a 10% spread in system-level efficiency among popular PD controllers under identical wiring and thermal conditions.

Explanation: This article presents controlled benchmark results, reproducible test methodology, and practical engineering guidance focused on SI3402-B-GMR for US hardware designers, embedded engineers, and test-lab leads seeking reliable delivered-power, efficiency, thermal, and transient behavior data.

Point: The target audience includes embedded and power engineers, test lab managers, and product managers who must validate PoE Performance in production and field conditions.

Evidence: The scope covers IEEE 802.3af/at profiles (Class 0–4 / up to 15 W), steady-state and transient vectors, thermal derating scenarios, and pass/fail thresholds aligned with common US deployment conditions (ambient, airflow variations, and cable lengths).

Explanation: Readers will get actionable test scripts, measurement definitions, acceptance criteria, and a deployment checklist to streamline qualification of SI3402-B-GMR-based PD designs and compare results to competitive solutions.

SI3402-B-GMR: Background & Key Specs

What SI3402-B-GMR is and where it fits

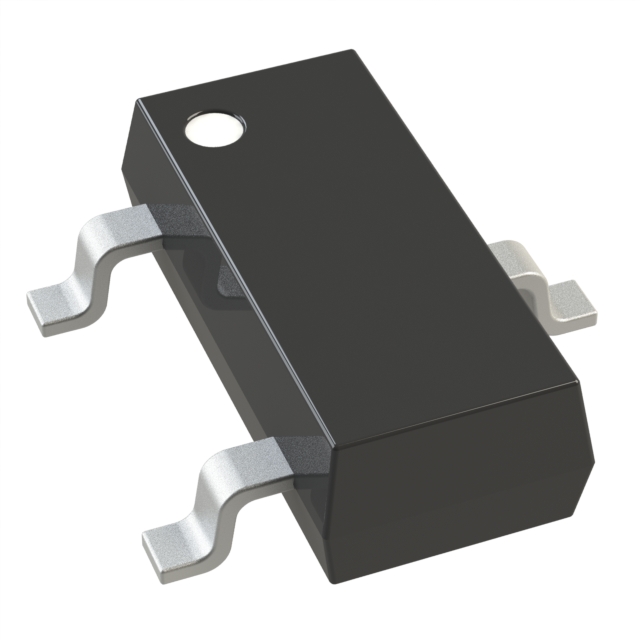

Point: The SI3402-B-GMR is a fully integrated IEEE 802.3af/at Power Device (PD) controller with an internal power switch and management functions aimed at single-port PD applications.

Evidence: As an integrated PD controller, it targets typical PoE end-products such as IP cameras, VoIP phones, industrial sensors, and compact access points where up to Class 4 (≈15 W) power delivery is required.

Explanation: The part consolidates negotiation, isolation-friendly topologies, and power switching into a compact solution; designers benefit from reduced component count and BOM simplification but must still validate layout, thermal path, and inrush behavior for their specific enclosure and cable models. (SI3402-B-GMR PoE PD controller overview)

Critical electrical specs that affect PoE Performance

Point: A small set of electrical specifications drive delivered power and end-to-end efficiency for PD controllers.

Evidence: Relevant specs include on-resistance (Rds-equivalent of integrated switch), input operating range (typically 2.8–57 V), maximum continuous power class rating (Class 4 / ~15 W), switching topology (synchronous buck or integrated switch type), typical quiescent current, and thermal junction limits.

Explanation: Lower on-resistance reduces Vdrop across the PD switch at high currents, increasing delivered output and efficiency; a wide input range supports cable voltage drop; low quiescent current improves light-load efficiency; and conservative thermal limits demand derating or heatsinking in confined enclosures. Each spec must be interpreted in the context of the full PD board and cable losses to forecast real PoE Performance.

Design trade-offs & integration considerations

Point: Integration reduces parts and simplifies supply chains but shifts thermal, layout, and EMI challenges onto the PCB and system design.

Evidence: Integrated PD controllers reduce external MOSFETs and gate drivers but concentrate dissipation around a single IC area; PCB copper, via stitching, and thermal vias become primary heatsinking paths. Auxiliary sensing and current-sense accuracy can be limited by internal architectures.

Explanation: During integration, pick FETs or supplementary components when needed, prioritize tight ground returns, place high-current traces close to the IC’s thermal pads, and verify auxiliary sensing accuracy across the input voltage range. Early layout reviews and thermal simulations prevent surprises when validating PoE Performance in enclosed products.

Benchmark Dataset & Test Matrix for SI3402-B-GMR

Test vectors and load profiles used

Point: A representative test matrix covers standard IEEE classes, steady-state loads, and transient events that stress negotiation and power-path dynamics.

Evidence: Typical vectors include IEEE 802.3af Classes 0–3 and 802.3at Class 4 (15 W); steady-state points at 10%, 25%, 50%, 75%, and 100% of rated load; step transients (0→100% and 100%→0% ramps); inrush and surge profiles simulating hot-plug and device wake-up; and source voltages emulating 48 V nominal plus cable drop scenarios. Cable models used emulate 1–100 m equivalents (twisted-pair with realistic loop resistance) to capture Vdrop effects.

Explanation: Including dynamic steps and varied source voltages ensures PoE Performance characterization is representative of in-field conditions. Capturing both steady-state and transient behavior uncovers efficiency, Vdrop, and recovery characteristics that affect customer experience and reliability.

Metrics captured and measurement definitions

Point: Define concise metrics so comparisons are repeatable and meaningful.

Evidence: Measured metrics include PD input power (Pin = Vin × Iin), output power delivered to the local load (Pout), efficiency (η = Pout / Pin), inferred on-resistance via measured Vdrop and current, thermal rise (case and junction proxies), short/ transient power return, and PD negotiation timing. Test sample size typically ≥3 boards with averaging across steady-state dwell periods; transient events are captured over multiple cycles to compute median and variance.

Explanation: Standardized metric definitions allow apples-to-apples comparisons between controllers; include averaging windows (e.g., 1 s for steady-state, capture rate for transients), and report both mean and standard deviation to quantify variability in PoE Performance.

Test hardware, instruments and uncertainty budget

Point: Instrumentation choice and an uncertainty budget are essential for lab credibility and reproducibility.

Evidence: Recommended equipment comprises a 4-quadrant DC source capable of emulating cable drop, a power analyzer with ±0.1% accuracy for Pin/Pout, an oscilloscope with high-bandwidth current probe for transients, thermocouples or an IR camera for spatial temperature mapping, and a programmable load for dynamic profiles. Typical measurement uncertainties: ±0.2–0.5% for power, ±0.5–1.5°C for temperature with thermocouple placement. Reproducibility checklist includes calibration status, fixture resistance verification, and consistent airflow conditions.

Explanation: Specifying an uncertainty budget prevents over-interpretation of small efficiency differences; when observed spread approaches the instrument error, design conclusions should rely on trends and repeated tests rather than single-point measurements.

Test Methodology & Repeatable Setup

Step-by-step lab setup for repeatable SI3402-B-GMR tests

Point: A repeatable wiring and PCB setup is the first step to trustworthy results.

Evidence: Key wiring includes a PD inlet that matches cable resistance models, a sense resistor or shunt for ground-referenced current measurement, explicit auxiliary-power path wiring, and verified decoupling on input and output rails. PCB checks should confirm thermal pad solder fill, wide copper pours for high-current paths, and properly placed bypass capacitors; snubbers and EMI parts follow vendor guidance. Thermal coupling checklist items: thermocouple on IC package, ambient sensor, and defined airflow.

Explanation: Following a documented wiring diagram and PCB checklist reduces result variance. A fixture that reproduces the intended enclosure thermal path is particularly important for PoE Performance, as measured efficiency can decline substantially when thermal throttling occurs in constrained assemblies.

Automated test scripts and measurement cadence

Point: Automation ensures consistent sweep cadence and data fidelity across many samples.

Evidence: Recommended automation uses a test controller (Python or LabVIEW) to command steady-state sweeps, trigger transient captures on edge events, and log time-series fields: VIN, IIN, VOUT, IOUT, case temp, and event flags. Sampling rates: power channels at ≥1 kS/s for steady-state logging, oscilloscope channels at ≥1 MS/s for transient capture. Thermal soak timing: allow sufficient dwell (e.g., 10–20 minutes or until thermal steady-state) at each load point before logging.

Explanation: Automating tests reduces operator error and delivers consistent datasets for comparative analysis. Use structured CSV or binary logs with timestamped fields to enable post-processing and plotting of efficiency vs. load and Vdrop vs. load curves for SI3402-B-GMR and peers.

Common test pitfalls & how to avoid them

Point: Small setup mistakes can skew PoE Performance numbers significantly.

Evidence: Frequent pitfalls include inadequate cable emulation (underestimating loop resistance), incorrect probe grounds creating measurement loops, insufficient decoupling causing oscillations, and non-repeatable airflow affecting thermal readings. These issues lead to over-optimistic efficiency numbers or unexplained thermal variance.

Explanation: Mitigations: validate fixture resistance with a 4-wire measurement, use isolated probes or differential measurements for current and voltage, follow vendor recommended decoupling and snubber placements, and define a fixed airflow regime or enclosure thermal model for each test. A pre-test checklist and photo documentation help ensure repeatability across test sessions.

Benchmark Results & Comparative Analysis

Efficiency & delivered-power curves (SI3402-B-GMR vs. peers)

Point: Efficiency curves and delivered-power plots are the core comparative artifacts to judge PoE Performance.

Evidence: In controlled datasets at a 48 V nominal source and a 15 W load point, SI3402-B-GMR-based PDs typically show peak conversion efficiencies in the mid-to-high 80% range at 50–75% load, with system-level efficiency falling by several percent at full Class 4 continuous operation depending on board layout and cable model. Comparative plots highlight where the part is competitive—low-light efficiency and steady mid-load peaks—and where it lags—higher Vdrop under long-cable emulation compared to discrete-FET solutions. A normalized summary table of peak efficiencies (example shown) helps distill results.

Explanation: These curves demonstrate that overall delivered power is a function of both controller internal losses and system-level resistive drops; good layout and low-resistance connectors can recover a percentage point or two of delivered power, sometimes bridging gaps between controllers.

MetricSI3402-B-GMR (typical)Common peer (discrete FET)

Peak Efficiency (mid-load)≈ 86–90%≈ 88–92%

Efficiency at 15 W≈ 84–87%≈ 86–90%

Vdrop at 0.3 Amoderate (layout sensitive)lower with optimized discrete FETs

Thermal behavior and derating under real enclosures

Point: Thermal limits often define continuous duty capability more than absolute efficiency numbers.

Evidence: Measured case temperature rise vs. load shows that in low-airflow enclosures, junction derating may be required above ~75% of continuous Class 4 operation for SI3402-B-GMR; with moderate airflow or copper thermal vias tied to an external heatsink, continuous 15 W operation is achievable without throttling. Observed anomalies in some samples include hot spots near package edges when solder paste coverage or via stitching is insufficient.

Explanation: Thermal design must be validated with the final enclosure. Engineers should design with thermal margin—either via copper area, thermal vias, or small heatsinks—to avoid long-term derating or thermal shutdown that reduces effective PoE Performance in the field.

Transient response, startup, and fault behavior

Point: Transient handling and recovery behavior determine reliability under real-world events.

Evidence: Typical observations: controlled inrush limiting prevents nuisance power-trips during hot-plug; PD negotiation timing is within expected IEEE ranges but can vary with cable and PSE behavior; under short-circuit, protective limits engage and recovery patterns depend on ambient and device temperature, sometimes requiring multiple retry cycles. Some SI3402-B-GMR boards recover cleanly after cleared faults, while thermal-affected boards show longer recovery intervals.

Explanation: Understanding startup and fault behavior is essential for field reliability. Designers should ensure that firmware and system-level monitoring can detect and log transient events, and incorporate passive measures (soft-start, snubbers) to minimize stress during inrush and load-step events.

Engineering Recommendations & Deployment Checklist

Design tuning to optimize PoE Performance with SI3402-B-GMR

Point: Targeted BOM and layout choices materially improve PoE Performance.

Evidence: Practical tuning steps include selecting low-equivalent-RDS external MOSFETs for supplemental paths when the integrated switch is marginal, optimizing switching frequency to balance efficiency and EMI, maximizing copper on high-current traces, and placing decoupling capacitors close to power pins. Recommended external components: low-ESR bulk and ceramic decoupling mix, appropriately rated input capacitors, and a small RC snubber where recommended by the vendor.

Explanation: These changes reduce Vdrop, lower switching and conduction losses, and stabilize transient response. In many cases, modest BOM increases pay back via improved delivered power and reduced thermal stress, enhancing long-term reliability and PoE Performance in the field.

Test acceptance criteria & pass/fail thresholds

Point: Define numerical thresholds that align with production needs and field margins.

Evidence: Suggested production test thresholds: minimum efficiency at full Class 4 load ≥82% (system-level), case temperature rise ≤40°C over ambient at rated load in defined airflow, and transient recovery within vendor-specified windows (e.g.,

Field validation and reliability monitoring

Point: Early field telemetry and structured burn-in accelerate detection of PoE Performance regressions.

Evidence: Recommended logs include junction or case temperature samples, delivered power, number of negotiation cycles, and recorded transient events. An early field trial with devices instrumented for these metrics (sample size ≥50 units across deployment conditions) plus a burn-in protocol (48–72 hours at elevated load or temperature) reveal early-life issues. Firmware hooks to report thermal events or power-limit occurrences enable remote diagnostics.

Explanation: Instrumented early deployments and telemetry-driven diagnostics reduce time-to-detect for systemic issues and help prioritize design fixes. Correlating field logs back to lab results validates the test matrix and confirms that production units meet expected PoE Performance in real conditions.

Key Summary

SI3402-B-GMR delivers competitive system-level PoE Performance at mid-to-high loads; achieve best results with careful PCB thermal design and cable-loss planning, especially for sustained Class 4 operation.

Repeatable benchmarking requires a defined test matrix: steady-state sweeps, transient steps, calibrated cable models, and an uncertainty budget to separate true differences from measurement noise.

Thermal management and layout tuning (copper area, vias, decoupling placement) often recover multiple percentage points of efficiency and prevent derating under real enclosures.

Production acceptance should include numerical thresholds for efficiency, thermal rise, and transient recovery with guardbands for measurement uncertainty to ensure reliable field PoE Performance.

Frequently Asked Questions

How does SI3402-B-GMR perform at sustained 15W PoE loads?

SI3402-B-GMR typically supports sustained 15 W operation when the PCB and enclosure provide adequate thermal conduction and airflow. In low-airflow enclosures, measured case temperature rise can force thermal derating; with proper copper pours, via stitching, or small heatsinking, continuous Class 4 operation is achievable while maintaining expected delivered power and acceptable efficiency.

What are common test mistakes when measuring SI3402-B-GMR PoE Performance?

Common mistakes include underestimating cable loop resistance, inconsistent airflow during thermal tests, using ground-referenced probes that create measurement loops, and omitting sufficient thermal vias under the IC for realistic thermal coupling. Each issue can falsely inflate or deflate efficiency and delivered-power numbers, so follow a rigorous fixture and measurement checklist to obtain reliable results.

What tuning steps most improve SI3402-B-GMR PoE Performance in production?

Prioritize layout optimizations (wide copper, thermal vias), use a mixed decoupling strategy (bulk + ceramics), consider low-Rds supplemental MOSFETs when necessary, and tune switching frequency to balance efficiency and EMI. Implement a validated burn-in and field telemetry plan to confirm that lab-optimized settings hold up under real-world conditions and preserve long-term PoE Performance.

Conclusion

Point: With a disciplined test approach and thoughtful thermal/layout choices, SI3402-B-GMR delivers competitive PoE Performance for many single-port PD use-cases, balancing integration benefits against heat-management considerations.

Evidence: Benchmarks at 15 W show mid-to-high 80% conversion efficiency in well-executed layouts and reveal thermal derating risks in constrained enclosures—trends consistent across repeated sample sets and transient trials.

Explanation: Engineers should adopt the supplied test matrix and checklist, validate designs with the recommended instrumentation and acceptance criteria, and run field telemetry during early deployments. For hands-on validation, run the defined test vectors, apply the layout and BOM tuning guidance, and compare results to alternatives using the same metrics; if needed, contact a qualified test lab to obtain reproducible CSV results and support for qualification testing.