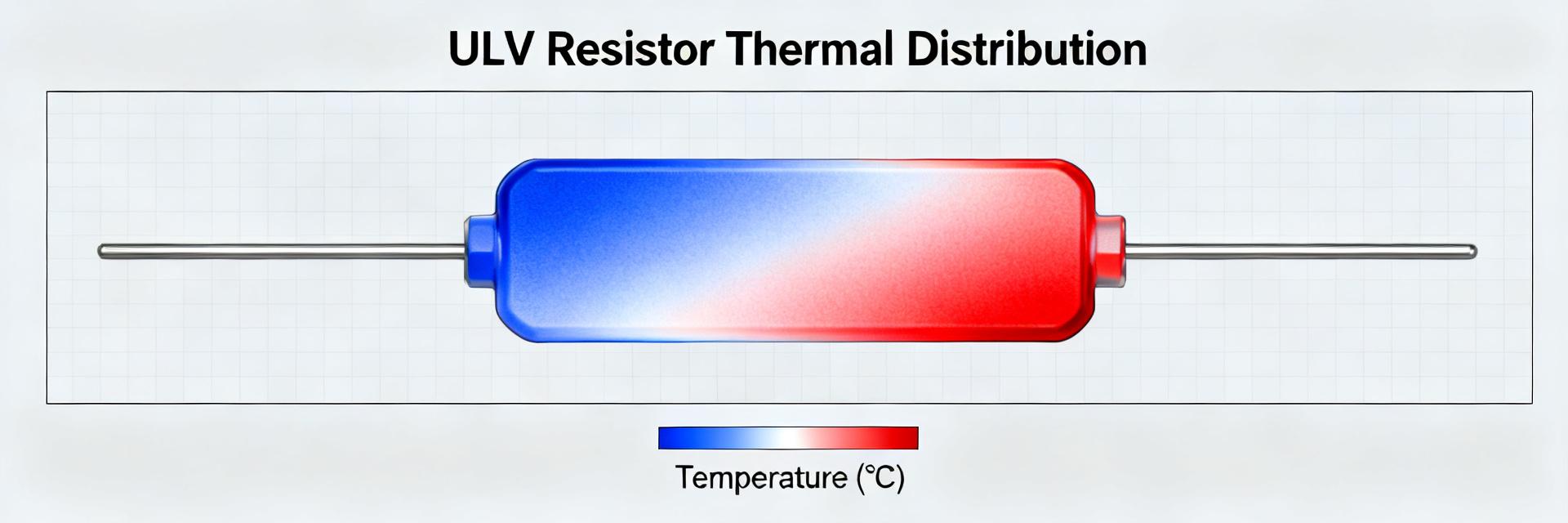

A professional technical analysis for power electronics designers and engineers. Rated 120 W continuous with 750 J pulse energy and FL=500 flying leads — what does that mean in practice? This datasheet deep dive translates those headline numbers into selection, mounting and test actions for power electronics. Recommended reading time: ~6–8 minutes. Target audience: power electronics designers, test engineers and procurement professionals who must size, verify and deploy a high-energy wirewound resistor safely. The goal is a line‑by‑line, application‑focused interpretation of the datasheet so engineers can act with confidence. 1 — Quick overview & top-line specs (background introduction) Key electrical ratings to highlight Point: Extract the essential electrical ratings first so you can filter candidates quickly. Evidence: Nominal continuous power 120 W; pulse energy rating 750 J; resistance tolerance example J = 5%; lead style indicated by code FL=500 (flying leads 500 mm). Explanation: these three figures (continuous power, pulse energy, and lead style) determine whether the part meets thermal, transient and mechanical constraints for your subsystem. Parameter Typical Value / Note Continuous power 120 W (at reference ambient) Pulse energy 750 J (single pulse safe energy) Resistance & tolerance Range per code; tolerance J = 5% Lead style FL=500 → flying leads, 500 mm Package Metal-clad, wirewound Mechanical form factor & connectors Point: The package is a metal-clad wirewound with long flying leads by code. Evidence: FL=500 denotes 500 mm insulated leads suitable for remote mounting. Explanation: use the flying leads to place the resistor away from sensitive components or to connect to busbars; verify the datasheet dimension diagram for mounting hole positions and clearance so thermal path and strain relief are correct. Suggested alt text for dimension diagram: "ULH 120 750 J FL=500 dimensions diagram". 2 — Electrical performance deep-dive: continuous, pulse & overload behavior (data analysis) Continuous power, derating & ambient dependency Point: Continuous rating must be derated with ambient temperature and mounting. Evidence: rated 120 W at the datasheet reference temperature (often 40°C). Explanation: if the datasheet provides a linear derating, read power vs. ambient curve; if not, apply a conservative derating rule. Example calculation: assuming a derating of 1% per °C above 40°C, at 60°C ambient allowable power ≈ 120 W × (1 − 0.20) = 96 W. Action: replicate the datasheet derating curve and use the conservative example when the manufacturer curve is unavailable. Pulse energy, surge handling & safe operating area Point: Pulse energy (750 J) governs single‑event heating and safe repetition rate. Evidence: datasheet pulse rating normally specifies energy per pulse and recommended repetition limits. Explanation: convert pulse energy to temperature rise by assuming a thermal mass and specific heat for the hot spot. Worked example: assume thermal mass m = 0.05 kg and c = 450 J/kg·K → ΔT ≈ 750 J / (0.05×450) ≈ 33°C. Apply a 20–30% safety margin: design for ≤25°C rise per pulse and allow cooling interval per datasheet repetition guidance. 3 — Thermal management, mounting & derating practices (method guide / data analysis) Thermal resistance, heatsinking and mounting best practices Point: Minimize thermal resistance from hotspot to ambient to sustain continuous power. Evidence: datasheet may list Rth or provide power vs. temperature curves; if not, approximate using measured derating. Explanation: recommended mounting: flat, clean metal surface; use thin, high‑conductivity thermal interface compound if permitted; torque screws to specified range and use star washers for electrical and mechanical security. Mounting checklist below ensures repeatability. Surface flatness: ≤0.1 mm over contact area. Thermal compound: thin, electrically insulating if required. Screw torque: follow datasheet—typ. 1.5–2.5 N·m for M4 fasteners (verify part drawing). Isolation: use mica or thermal pads when electrical isolation is needed. Environmental limits & reliability considerations Point: Environmental stress shortens life if not addressed. Evidence: datasheet lists operating temperature, humidity and vibration limits. Explanation: for harsh environments, apply additional derating (e.g., 10–30% power reduction), and mandate pre-deployment thermal cycling and vibration acceptance tests. Track failures like corrosion, lead fatigue and insulation breakdown. 4 — Application scenarios & selection checklist (case-focused + method) Typical use cases and why this resistor fits Point: Match resistor specs to application energy/time profile. Evidence: common applications include dynamic braking, load banks, inrush limiting and test stands where high single‑pulse energy and moderate continuous dissipation are required. Explanation: for dynamic braking prioritize pulse energy and peak voltage; for continuous load banks prioritize steady power and heatsinking. Use safety margins (20–30%) on pulse energy and continuous power when mapping to application. Substitution rules and equivalent selection guidance Point: Know which parameters are non‑negotiable when substituting. Evidence: pulse energy, peak voltage and lead style typically cannot be compromised. Explanation: tolerance or physical size can sometimes trade off; when in doubt choose higher pulse energy and at least equal continuous power, or parallel multiple resistors ensuring equal current sharing and consider added ESR and inductance effects. Procurement checklist: required power & pulse, lead length FL=500, clearance and required certifications. 5 — Installation, verification testing & maintenance checklist (action recommendations) Pre-installation and on-bench validation tests Point: Verify each unit on receipt before integration. Evidence: datasheet test recommendations usually include insulation resistance and resistance tolerance measurements. Explanation: standard checks: visual inspection, megohm insulation test if applicable, DC resistance measured at controlled temperature, and one or two low‑energy pulses while monitoring temperature with a thermocouple on the metal case and an oscilloscope to verify pulse waveform. Pass/fail: resistance within tolerance; temperature rise per pulse within expected range (allowing safety margin). Long-term maintenance, monitoring and failure modes Point: Implement periodic checks to catch degradation early. Evidence: common failure modes are overheating, lead fatigue and corrosion. Explanation: monitoring plan: monthly visual inspection, quarterly electrical check (resistance drift), annual thermal imaging under nominal load. Replace after significant resistance drift (>5% for J tolerance) or any overload event that produced abnormal temperature excursions. Summary (Actionable Takeaways) This practical, datasheet‑driven guide helps engineers select, mount and test the ULH 120 750 J FL=500 power resistor by translating specs into repeatable engineering actions. Derating matters: recalculate continuous allowable power for your ambient and mounting to avoid overstress and shortened life. Pulse planning: convert 750 J pulses into expected temperature rise with conservative thermal mass assumptions and include a 20–30% safety margin for repeat events. Mounting & testing: follow a torque/flatness checklist, validate units with low‑energy pulses and thermocouple monitoring, and log results for traceability. Call to action: download the datasheet, run the worked examples provided here, and use the checklists before installation. FAQ How should I verify a new unit from the datasheet on the bench? Run a visual inspection, measure DC resistance at controlled temperature, perform an insulation check if required, then apply one or two low‑energy pulses while monitoring case temperature with a thermocouple and pulse shape with an oscilloscope. Use pass/fail thresholds: resistance within tolerance, and temperature rise per pulse within expected datasheet or calculated limits. What is a safe repetition rate for 750 J pulses? Datasheets often limit repetition based on cooling; if unspecified, assume conservative duty: single or very low repetition (e.g., one pulse per minute) until verified by temperature testing. Measure cooling curve after a representative pulse and establish the interval that returns the part to near‑baseline temperature before the next event. When should I replace the resistor in service? Replace after any overload event that causes abnormal temperature excursions, or if resistance drifts beyond tolerance (example: >5% for J tolerance). Also replace on signs of mechanical damage, lead fatigue, corrosion, or after a specified number of thermal cycles if defined by your reliability plan.