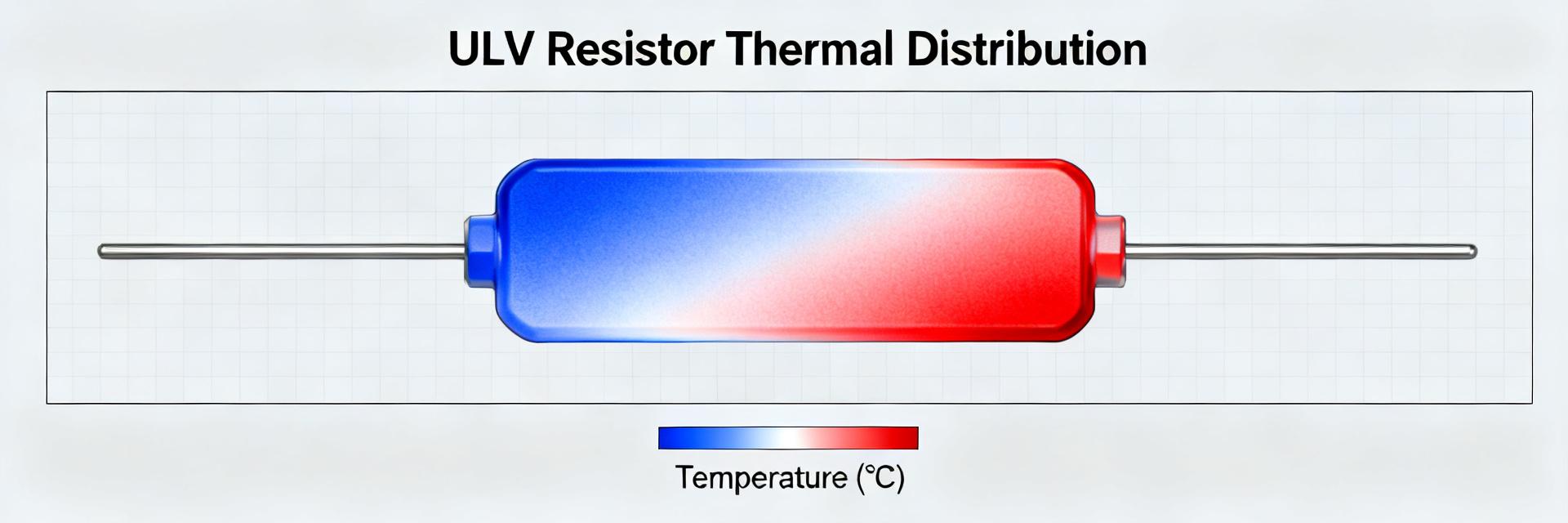

Thermal Engineering High Power Component Field and datasheet test points indicate continuous case-limited ratings approaching 500 W at a specified reference case temperature; transient pulses can exceed that by several times but demand strict cooling and duty-cycle limits. This data-driven hook frames why precise thermal data and derating practice are decisive for ULV1000 resistor reliability and overall system safety. The purpose of this guide is to synthesize current thermal data, clarify derating practice, and provide actionable measurement and installation guidance engineers can apply when designing with this family. It focuses on thermal data interpretation, test methods, and practical derating rules for robust system integration. Background: ULV1000 resistor — key specs & thermal basics What the ULV1000 resistor is designed for Point: The ULV1000 resistor is a high-power metal-clad/wire-wound class typically used in load banks, dynamic braking, and power conversion. Evidence: Manufacturer datasheets and independent lab reports list power classes in the 600–1200 W range with resistance values spanning low-ohm to kilo-ohm classes. Explanation: Construction favors a heavy ceramic case with large terminals for conduction; common mounting styles include chassis bolt-down or through-bushing fixation to support heat transfer and secure mechanical load. Thermal fundamentals relevant to ULV1000 performance Point: Thermal behavior depends on thermal resistance (°C/W), reference case temperature, and heat paths. Evidence: Thermal data in test reports distinguishes case vs. ambient ratings and shows that conduction to the chassis and forced convection dramatically raise continuous power capability. Explanation: Use ΔT/P to estimate °C/W: steady-state depends on airflow and mounting; transient pulses depend on time constant (τ) and heat capacity—test setups often specify a reference case temperature measured at a calibrated thermocouple spot. Data analysis: Latest thermal data, test results & derating curves Conceptual Derating Profile: Power vs. Case Temperature 100% Power 25°C T-ref (Nominal) T-max Note: Actual curve shifts based on mounting substrate and airflow velocity. Interpreting continuous power vs. temperature (derating curves) Point: Derating curves define a constant-power plateau to a reference case temperature, then a linear decline to an ambient cut-off. Evidence: Typical thermal data presents allowed power at reference case temp (e.g., 500 W) and a slope reducing allowed power by a set W/°C to a safe ambient limit. Explanation: Read the curve by locating your expected case temperature under load; choose the intersection to determine safe continuous power. Mounting choices that lower case temperature (heat sink, conductive pad) shift the operating point to higher allowable power. Transient/pulse thermal behavior and time constants Point: Pulse capability depends on energy, pulse width, and the resistor thermal time constant. Evidence: Test pulses show short pulses (milliseconds to seconds) can allow several kJ without exceeding ΔT limits, while cumulative heating reduces headroom for repeated pulses. Explanation: Use the resistor's thermal capacitance and τ to model temperature rise: for a single pulse, allowable energy ≈ C·ΔTmax; for repetitive pulses, ensure sufficient off-time for cooling to avoid thermal runaway. Apply duty limits conservatively for in-enclosure applications. Measurement & validation: how to collect reliable thermal data Recommended test setup & instrumentation Point: Repeatable thermal characterization requires specified sensor placement, controlled ambient, and adequate instrumentation. Evidence: Best practice uses a thin-film thermocouple on the indicated case spot, an IR camera for distribution checks, a stable power source, and a data logger sampling at ≥1 Hz. Explanation: Mount the thermocouple with thermal paste at the reference point called out by the datasheet, control ambient (±1°C), and document airflow. Safety note: start at low power and step up while monitoring temperature trends and chassis conduction paths. Data processing: extracting thermal resistance and validating derating Point: Extract °C/W and validate derating curves from steady-state and transient tests. Evidence: Compute thermal resistance as Rth = ΔT / P after steady-state is reached; for pulses, fit exponential temperature response to obtain τ and effective capacitance. Explanation: Apply a conservative design margin (typical practice: 20–30%) to measured limits when specifying operational power. Record raw logs, photos of setup, and spreadsheet columns for time, voltage, current, case temp, and ambient for qualification traceability. Practical case study: applying thermal data to a system design Design scenario & constraints Point: A realistic constraint example clarifies derating decisions. Evidence: Consider a braking module requiring 400 W bursts inside a sealed enclosure with 40°C ambient and limited airflow; space permits only chassis-mounted resistors. Explanation: Given enclosure heat buildup, designers must assess whether the ULV1000 resistor allowed continuous power at the case reference temperature can sustain the duty cycle, or if additional heat sinking or forced ventilation is mandatory to avoid exceeding thermal limits. Step-by-step derating and final specification Point: Apply the derating curve and pulse rules to derive final spec. Evidence: Read the derating curve: at 40°C and your measured case-to-ambient delta, continuous allowed power drops; add pulse energy allowance per τ and ensure off-time for recovery. Explanation: If the curve indicates allowable continuous power <400 W under current mounting, specify cooling (e.g., 0.5 m/s forced airflow or a conductive pad to chassis) to raise allowable power, or derate the resistor to a conservative continuous rating (e.g., 300 W) with a 25% safety margin and documented pulse limits. Action checklist & installation best practices Category Action Item Recommendation Pre-deployment Datasheet Review Confirm T-ref location and derating slope. Installation Mounting Integrity Use thermal pads and specified torque values. Maintenance Thermal Inspection Periodic IR scans for hotspots or corrosion. Summary Understand primary thermal limits: Start from the datasheet reference case rating and interpret the derating slope to set continuous power limits within your enclosure. Use measured thermal data: Extract °C/W from steady-state and τ from transient tests, then apply a conservative design margin. Apply practical controls: Consider conductive mounting, forced airflow, or reduced duty cycle to meet system requirements. Frequently Asked Questions Q: How should I derate a ULV1000 resistor for elevated ambient temperature? Derating should follow the published curve: determine the case temperature under your mounting and ambient, find the corresponding allowed power, and apply a safety margin (20–30%). If the required power exceeds the derated allowance, add conductive mounting or forced airflow to lower the case temperature before increasing power. Q: What test setup yields reliable ULV1000 resistor thermal data? Use a calibrated thermocouple at the datasheet’s reference point, control ambient, log voltage/current and temperature until steady-state, and capture IR images for hotspot checks. For pulse tests, record pulse width, duty, and temperature recovery to extract τ and allowable pulse energy. Q: What are recommended in-field checks to ensure continued ULV1000 resistor reliability? Perform periodic IR scans under representative load, verify terminal torque and mounting integrity, and compare measured temperatures to expected values. If temps rise over time beyond tolerance, investigate airflow blockage, corrosion, or changes in conduction path and re-qualify with a short thermal test. © Professional Thermal Engineering Series | Reliable High-Power Resistance Design