The HEIKIT1020050E29 kit appears simple on a parts list, but close inspection of its numerical entries reveals whether it will install cleanly and survive long-term thermal stress. This data-driven intro highlights which mechanical and thermal numbers to extract from the HEIKIT1020050E29 datasheet, and sets expectations for procurement and test teams when they verify fit, finish, and functional compatibility.

In this guide the terms datasheet and specs are used to mean the explicit numerical tables and drawings you must capture: dimensions, material/finish calls, thermal notes, and any mounting torque or clearance recommendations that affect resistor assemblies and chassis integration.

1 — Background: what HEIKIT1020050E29 is and why its specs matter

1.1 — Function & typical use cases

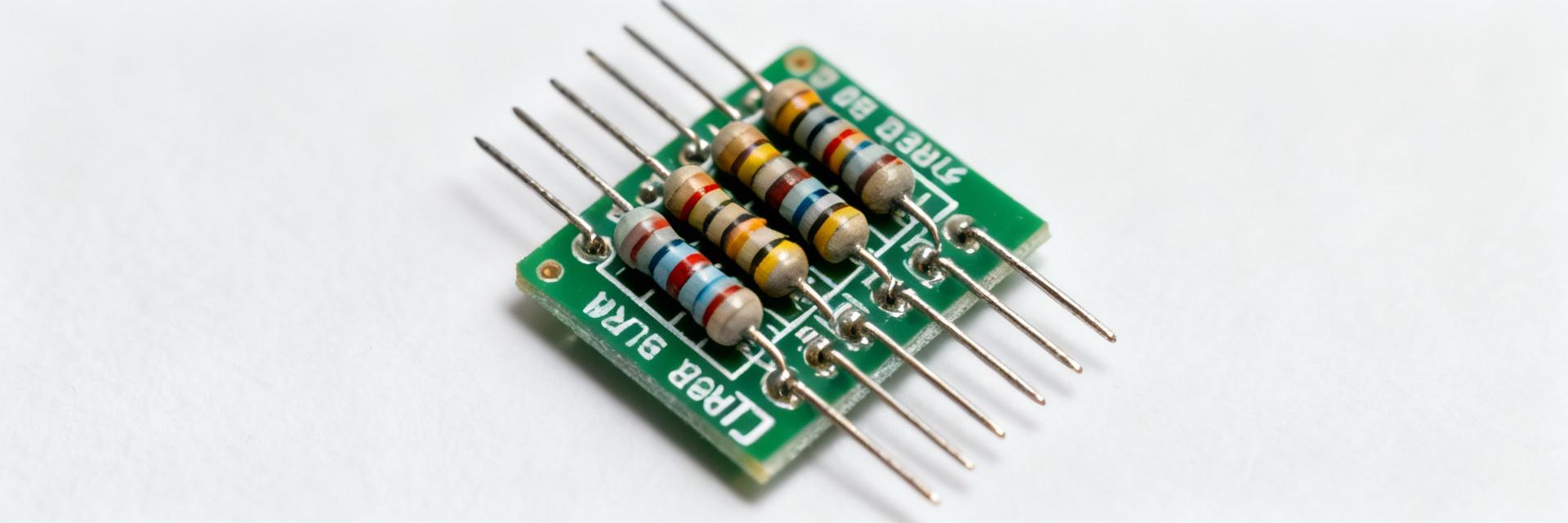

Point: The HEIKIT1020050E29 serves as mounting hardware for resistor assemblies and provides mechanical support and thermal conduction paths where required. Evidence: Typical use is to secure PCB-mounted resistors or to form part of high-density resistor banks. Explanation: In practice the bracket’s footprint, standoff height, and hole pattern determine whether a resistor lands within specified creepage and clearance while also allowing heat to flow into the chassis.

1.2 — Common variants and part-number clues

Point: Kit suffixes and variant numbers often encode orientation, finish, and fastener type. Evidence: Datasheet ordering tables typically map suffixes to finish (e.g., passivated, plated) and to included fasteners or washers. Explanation: When substituting, compare the suffix, the included fastener list, and package quantity; confirm the ordering section of the datasheet shows the exact kit contents and packaging to avoid surprises in assembly.

2 — Electrical & thermal specs deep-dive (data analysis) — HEIKIT1020050E29

2.1 — Thermal considerations and heat path

Point: Thermal behavior is governed by material conductivity, bracket cross-section, mounting orientation, and proximity limits. Evidence: The datasheet’s material callout and any recommended mounting orientation or clearance notes identify expected heat paths and maximum operating temperatures. Explanation: For high-power resistors, confirm bracket geometry provides a conductive path from resistor body to chassis; acceptance criteria include max operating temperature below component limits and recommended clearances to avoid hot spots.

2.2 — Electrical compatibility and clearance/creepage implications

Point: Electrical safety depends on insulation distances and dielectric properties where listed. Evidence: Look for stated insulation distances, dielectric materials, or maximum working voltage entries in the datasheet. Explanation: Translate those numbers into PCB layout decisions by ensuring board creepage and clearance exceed the datasheet minima and by verifying the bracket’s metal-to-metal or metal-to-insulator spacings match the resistor’s rated voltages.

3 — Mechanical specs and materials (data analysis)

3.1 — Interpreting mechanical drawings & dimensional tolerances

Point: Critical dimensions determine fit and tooling compatibility. Evidence: Extract hole spacing, bracket thickness, mounting hole diameter, standoff height, and overall footprint from the drawing and notes. Explanation: Account for tolerance callouts and datum references when designing PCBs and fixtures; create an inspection table to verify incoming parts against the datasheet geometry.

Nominal Dimension

Tolerance

Inspection Method

Hole spacing (center-to-center)

±0.1 mm

Calipers or optical comparator

Bracket thickness

±0.05 mm

Micrometer

Standoff height

±0.2 mm

Go/no-go gauge

3.2 — Material, finish, corrosion resistance, and torque specs

Point: Material and finish determine conductivity, corrosion resistance, and solderability. Evidence: The datasheet typically specifies base material and plating (e.g., stainless steel, zinc or nickel plating) and may note RoHS compliance. Explanation: If torque guidance is absent, use conservative default torque ranges for the specified fastener size and plan to validate torque in the lab; procurement should request material/finish certificates and plating thickness where corrosion or conductivity are critical.

4 — How to verify HEIKIT1020050E29 specs during procurement and test (method guide)

4.1 — Incoming inspection checklist (measurements & documentation)

Point: A concise incoming inspection prevents assembly delays. Evidence: Key checks include verifying part number and kit contents, confirming visual finish, measuring critical dimensions with calipers, and checking hole alignment against PCB templates. Explanation: Require material/finish certificates and dimensional drawings from suppliers; use calipers, micrometers, and an optical comparator for higher-volume audits, and record results in a traceable inspection report.

Verify part number and kit contents against the packing list.

Confirm surface finish and request material certificate if finish affects conductivity.

Measure hole spacing, standoff height, and thickness; accept only within datasheet tolerances.

Record supplier lot and date code for traceability.

4.2 — Bench tests and installation verification

Point: Practical bench validation ensures the bracket performs under expected stresses. Evidence: Conduct fit tests with a representative resistor and PCB, torque tests on fasteners, and thermal soak or cycling per industry-standard profiles. Explanation: Define pass/fail criteria (secure fit, no loosening at target torque, no deformation after thermal cycling) and log test conditions; if the datasheet omits torque values, derive safe torque from fastener standards and validate experimentally.

5 — Application example and sourcing checklist (case + action)

5.1 — Example: selecting the bracket for a high-density resistor array

Point: Selection requires matching resistor dimensions, power dissipation, and assembly method. Evidence: Walk through: define resistor size and required clearances, extract bracket footprint and standoff height from the datasheet, confirm material/finish for thermal conduction, and check packaging for automated placement. Explanation: At each step, annotate which datasheet value informed the choice—dimension table for fit, material callout for thermal path, and ordering table for kit contents—while noting common pitfalls like overlooked clearance to neighboring components.

5.2 — Quick procurement & compliance checklist

Point: A compact purchase checklist reduces back-and-forth with suppliers. Evidence: Items to request: confirmed part number and kit contents, material/finish certificates, RoHS status, packaging quantities, dimensional drawings, and any torque guidance. Explanation: Include short PO phrasing to lock requirements (example: “Supply HEIKIT1020050E29 per datasheet drawing X; include material certificate, plating spec, RoHS declaration, and packaging qty.”) and ask for acceptable alternates with equivalent specs.

Summary

Extract HEIKIT1020050E29 mechanical dimensions and tolerances from the datasheet drawing, and verify with calipers or optical comparison to ensure fit in the assembly footprint.

Confirm material and finish for thermal conduction and corrosion resistance; request certificates and validate plating when conductivity or reliability is critical.

Translate thermal notes into acceptance criteria: verify mounting orientation, clearance, and perform thermal soak/cycling to confirm heat path performance.

Use the procurement checklist to require dimensional drawings, material certificates, RoHS status, and packaging info to prevent assembly or compliance surprises.

Frequently Asked Questions

What are the critical HEIKIT1020050E29 specs to check before ordering?

Confirm the bracket’s hole spacing, standoff height, material/finish, and kit contents listed in the datasheet. These values determine fit, thermal path, and whether included fasteners meet assembly requirements; request certificates if finish or plating thickness is critical.

How should I interpret missing torque guidance in the HEIKIT1020050E29 datasheet?

If torque recommendations are absent, default to conservative torque values based on fastener size and material standards and validate them in a lab torque test. Record pass/fail criteria and update procurement language to require torque guidance for future lots.

Which datasheet specs most affect thermal performance of HEIKIT1020050E29-mounted resistors?

Material thermal conductivity, bracket cross-sectional area, mounting orientation notes, and minimum recommended clearances are primary. Verify these specs and run thermal soak or cycling tests to confirm expected temperature rise and mechanical retention under load.